SOPC实现4路高清摄像头视频处理的方案设计,软硬件架构

能互相补充,达到软件与硬件的最大优化,实现高速的图像特征提取效果。硬件加速SIFT算法为其在机器人定位,3D目标识别与跟踪等嵌入式领域的应用奠定了基矗

在图像匹配众多的算法中,SIFT算法对图像的光线亮度变化、尺度缩放以及旋转都能保持不变,对视角变化和噪声也保持一定程度的稳定性。适用于在海量数据库中进行快速实时的匹配,极具有极其广泛的应用范围与可观的发展前景。

4.可编程器件FPGA实现算法硬件加速

可编程器件FPGA极具设计灵活性,非常适合于高性能低成本的视频和图像系统设计及应用,视频特征提取的实时性对硬件要求很高,普通计算机CPU计算能力有限难以达到要求。基于FPGA平台,设计者可以选择如何实现软件代码中的每个模块,可以通过对算法实现的软硬件划分,利用FPGA中现有硬件资源等来加速软件代码中的瓶颈问题,使用FPGA硬件设计模块来提高SIFT算法的时效性。

本项目算法采用抗干扰、高精确度、应用前景广泛但计算相对比较大的SIFT,对其进行硬件实现极具研究价值。且有数据显示,100MHz处理一幅320×240大小图像SIFT特征点提取只需0.8ms。

5.SOPC(Systems On Programmable Chip)设计

本项目以FPGA芯片为实现目标器件,实现多路视频数据的采集处理,研究SIFT算法的硬件实现与加速,一定程度上提出有具有创新性的SOC体系结构。设计具有实时多路视频数据采集与复杂算法运算的数据处理的片上系统,把算法和控制集成到当个芯片中,为该类系统的产业化做了很好的理论与实践基础。在单系统芯片中实现大连数据采集、复杂数据处理是未来集成电路的发展趋势。

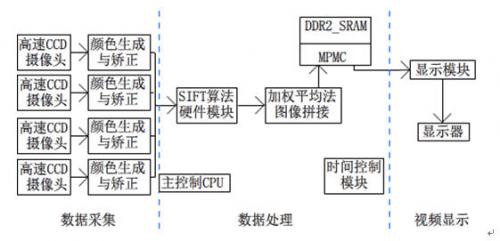

系统框图(jpg/gif格式的图像文件):

图1 系统框图

软件流程介绍(允许的格式doc,pdf,vsd,rar,zip):

本项目系统设计主要分三大模块,分别为数据采集与基本处理、视频帧图像的拼接处理以及视频显示输出。基于科研实验室项目经验,多路高速CCD摄像头数据采集与基本颜色生成与矫正存储功能模块以及单路标准视频显示模块以基本实现,本项目可在之前项目设计的基础上加以衍生升级应用。在此基础上,本项目更着重于实现SIFT算法的硬件实现与加速,实现实时视频的拼接。

数据处理有两大算法实现模块,为SIFT算法硬件模块与加权平均法图像拼接模块。

通过对SIFT算法的研究,在PC机上实现SIFT算法提取图像特征值,用加权平均法拼接图像。加权平均法在重叠区域的融合效果一般,会出现一些图像内容的模糊与重影,不过不是本项目的重点,多副图像的融合可以作为后续的发展及研究。在了解SIFT算法的基础上,采用HDL描述SIFT算法,实现硬件设计。

系统主要开发环境:Xilinx ISE Design Suite

拟采用的平台:Atlys Spartan-6 FPGA开发套件

系统所需额外设备:4台高速CCD摄像头(MT9P001_MI5100_DS)

项目测试的标准:

本项目最终实现环视系统的视频的实时采集与显示。

实现四路视频的采集,分辨率达到标清。通过SIFT算法特征点检测和平均加权法对帧图像拼接实现环视图像。4路视频帧图像之间衔接连贯,达到实时高效准确的视频拼接功能。

SOPC 视频处理 SIFT算法 FPGA Spartan-6 相关文章:

- 单片DSP处理器功能系统的SOPC技术设计(01-12)

- 基于DSP和SOPC数字信号发生器的设计(01-05)

- 基于Linux的SoPC应用系统设计(04-23)

- 基于DSP的实时数据处理系统浅析(02-28)

- 基于LXI总线的1553B通讯模块设计与开发(11-24)

- 双MicroBlaze软核处理器的SOPC系统设计(01-27)