函数信号发生器和示波器二合一仪器设计,提供源码

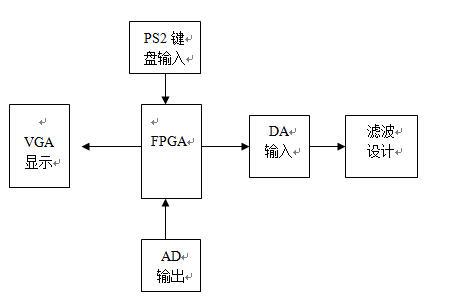

1.总体设计方案

1.1 主控制模块

方案一:采用单片机。单片机的应用较为广泛,但是单片机的处理频率达不到我们的要求。所以我们只能够使用处理速度较快的处理器。

方案二:采用Xilinx的FPGA来实现主控制器。Xilinx的FPGA的内部IP核可以方便的产生DDS波形,这样就方便我们能够更好的产生想要的波形。

所以采用方案二。

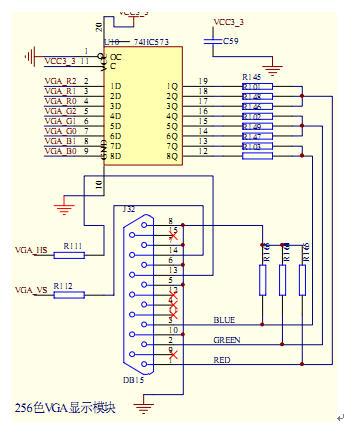

1.2显示模块

方案一:使用TFT触摸屏。彩屏有这样明显的优点:微功耗,尺寸小,超薄轻巧,显示信息量大,字迹美观,视觉舒适,但是对于FPGA来说,其实现对触摸屏的控制不能够较好的完成控制要求。

方案二:使用VGA显示。FPGA可以实现对VGA的控制。VGA的使用较为广泛,且价格在接收的范围之内。而且,对于FPGA来说,实现对VGA接口的控制比控制其他的显示器更加的方便和快捷。这就节省了我们的设计麻烦。

所以采用方案二。

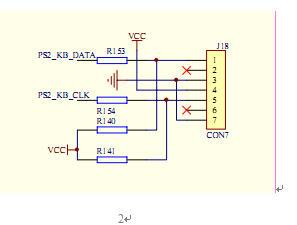

1.3 输入模块

方案一:使用矩阵键盘。矩阵键盘的编码较为简答,且可以实现较为复杂的控制。但是矩阵键盘的按键过少,不能够实现更多数据的输入。

方案二:使用PS2键盘。PS2键盘的控制更为简单,我们可以通过两根数据线精心数据的读取,且PS2键盘的设计更加符合我们设计要求,这就决定了PS2在本设计中的优势。

故采用方案二。

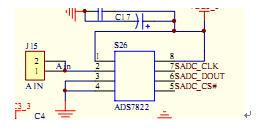

1.4 AD输出模块

ADS7822是一种单片高速12位逐次比较型A/D转换器, ADS7822内置双极性电路构成的混合集成转换显片,具有外接元件少,功耗低,精度高等特点,并且具有自动校零和自动极性转换功能,只需外接少量的阻容件即可构成一个完整的A/D转换器。所以该方案采用ADS7822作为AD输入的元器件。

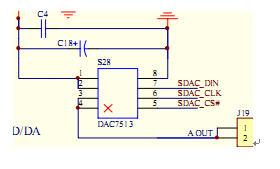

1.5 DA输出模块

DAC7513是8分辨率的D/A转换集成芯片。与微处理器完全兼容。这个DA芯片以其价格低廉、接口简单、转换控制容易等优点,在单片机应用系统中得到广泛的应用。D/A转换器由8位输入锁存器、8位DAC寄存器、8位D/A转换电路及转换控制电路构成。

2.程序设计

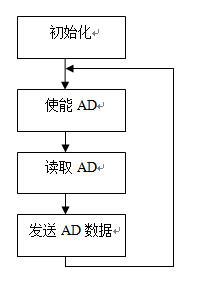

2.1 AD输出

--**********************分频进程*************************

process(clk)

variable cnt1 : integer range 0 to 100;

variable cnt2 : integer range 0 to 20;

begin

if clkevent and clk=1 then

if cnt1=100 then

cnt1:=0;

if cnt2=20 then

cnt2:=0;

clock=not clock;

if(cnt=3)then

cnt=0;

else

cnt=cnt+1;

end if;

else

cnt2:=cnt2+1;

end if;

else

cnt1:=cnt1+1;

end if;

end if;

end process;

--**************状态驱动进程**********************

sync :process(clock,reset)

begin

if(reset = 0) then

current_state = start;

elsif(clockevent and clock=1) then

current_state = next_state;

end if;

end process sync;

--***************adc驱动进程*******************

comb :process(current_state, intr)

begin

case current_state is

when start => --启动状态

next_state = convert;

cs = 0;

wr = 0;

rd = 1;

read_data = 0;

when convert =>--初始化

if(intr = 0) then

next_state = read1;

else

next_state = convert;

end if;

cs = 1;

wr = 1;

rd = 1;

read_data = 0;

when read1 =>--读状态1

next_state = read2;

cs = 0;

wr = 1;

rd = 0;

read_data = 1;

when read2 =>--读状态2

next_state = start;

cs = 1;

wr = 1;

rd = 1;

read_data = 0;

when others =>--其他状态

next_state = start;

end case;

end process comb;

--****************读取AD数据********************

get_data: process(clock,reset)

begin

if(reset = 0) then

p=0;

elsif(clockevent and clock=1) then

if(read_data = 1) then

p=conv_integer(data_i);

end if;

end if;

end process;

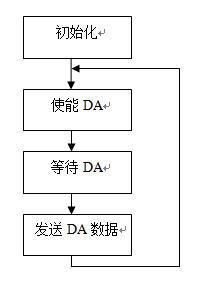

2.2 DA输出

--*********************65536Hz分频进程************************

process(clk)

variable cnt1 : integer range 0 to 762;

begin

if clkevent and clk=1 then

case cnt1 IS

WHEN 381 =>

cp_65k=1;

cnt1:=cnt1+1;

WHEN 762=>

cnt1:=0;

cp_65k=0;

cp_wr=0;

WHEN 20=>

cp_wr=1;

cnt1:=cnt1+1;

WHEN OTHERS=>

cnt1:=cnt1+1;

end case;

end if;

end process;

--*********************1kHz分频进程************************

process(cp_65k)

variable cnt1 : integer range 0 to 64;

begin

if cp_65kevent and cp_65k=1 then

case cnt1 is

when 32=>cp_1k=1;

cnt1:=cnt1+1;

when 64=>cnt1:=0;

cp_1k=0;

when others=>cnt1:=cnt1+1;

end case;

end if;

end process;

--**************DDS地址累加器进程**********************

PROCESS(cp_65k)

BEGIN

- 基于DSP的数字示波器用户图形化 (GUI) 的开发(05-16)

- 一种数字示波器的微处理器硬件电路设计(02-21)

- DSP在DSA70000系列示波器中的应用介绍(07-16)

- DSP在DSA70000系列示波器中的应用概述(08-11)

- 如何确定嵌入式设计可接受的抖动水平(04-15)

- 小型化、集成化——论SIP技术对减轻卫星载荷的重要性(10-20)