函数信号发生器和示波器二合一仪器设计,提供源码

IF(cp_65kEVENTANDcp_65k=1)THEN

--DDS累加器循环累加dds_m

IF dds_add65535 THEN

dds_add=dds_add+dds_m;

ELSE

dds_add=dds_add+dds_m-65536;

END IF;

END IF;

END PROCESS;

--***********************频率加减控制进程***************************

process(cp_1k)

VARIABLE keys:INTEGER RANGE 0 TO 127 :=0; --消抖累加器

begin

if cp_1k=1 then

case key is

when 10=> --频率加

if keys=127 then

keys:=0;

bell=1;

if dds_m=1000 then

dds_m=1;

else

dds_m=dds_m+1;

end if;

else

keys:=keys+1;

end if;

when 01=> --频率减

if keys=127 then

keys:=0;

bell=1;

if dds_m=1000 then

dds_m=1;

else

dds_m=dds_m-1;

end if;

else

keys:=keys+1;

end if;

when others=>bell=0;

end case;

end if;

end process;

end dac;

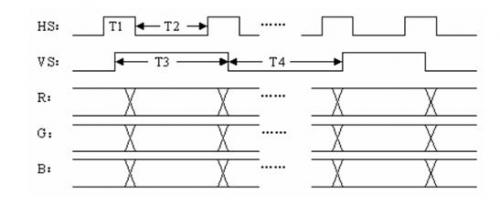

2.3 VGA显示

3.性能指标

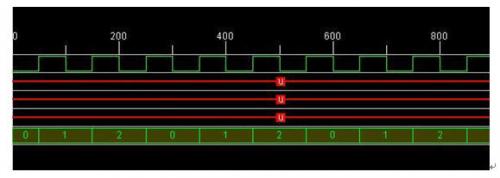

DA输出的波形

4.总结

经过了多日的努力,我们在本设计中基本实现了上述要求,并在有些功能方面提出了改进,使系统设计更加完善。在该设计中我们使用了FPGA作为主控器,但由于时间及器材条件的限制,本设计也存在不足,例如,测量范围不能达到更高的要求,测量精度也存在很大的提升空间。我们会在以后的学习中不断地弥补这些不足,完善测量系统设计。

- 基于DSP的数字示波器用户图形化 (GUI) 的开发(05-16)

- 一种数字示波器的微处理器硬件电路设计(02-21)

- DSP在DSA70000系列示波器中的应用介绍(07-16)

- DSP在DSA70000系列示波器中的应用概述(08-11)

- 如何确定嵌入式设计可接受的抖动水平(04-15)

- 小型化、集成化——论SIP技术对减轻卫星载荷的重要性(10-20)