Verilog语言:还真的是人格分裂的语言

是例子里面的8比特)的时候,输入和输出信号的skew(线间时延)可能会给设计带来麻烦。

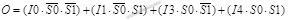

另一种常见的情况是输入不止有两个信号,或者说需要在不仅仅两个信号里面进行选择,这个叫做高阶数据选择器(一般吧SEL的比特数称为数据选择器的阶数)。通常输入个数是2的幂,此时选择信号SEL也就不仅是1比特信号了,这个很容易理解。在理论上,可以通过展开布尔逻辑表达式的方法,完成高速的高阶数据选择器。例如,2阶(也就是有4个输入信号,SEL为2比特变量)的随机选择的布尔逻辑表达式为:

其中,I0、I1、I2和I3为器件的输入,S0和S1为SEL信号的低比特和高比特。

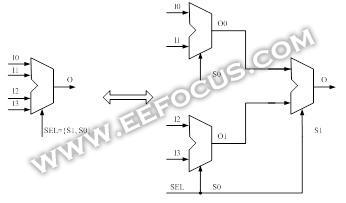

这个式子已经不简单了,如果是10阶神马的数据选择器,那样的式子的长度不难想象。所以,在工程上,一般利用低阶数据选择器的串联来实现高阶数据选择器。图4是一个用3个1阶数据选择器实现2阶数据选择器的例子。

图4 利用低阶数据选择器实现高阶数据选择器

对于高阶数据选择器的Verilog代码,一般建议利用case的形式。例如图3里面的2阶数据选择器可以用以下代码实现:

case (SEL)

2’b00:

begin

O = I0;

end

2’b01:

begin

O = I1;

end

2’b01:

begin

O = I2;

end

2’b11:

begin

O = I3;

end

endcase

这正是:

“

组合逻辑大融合,关键语法有心得。不论理论数学河,电路优化靠综合。

鄙人说书自有乐,撬行老僧沙弥哥。报告整理嫉妒惹,大乘渡人笑呵呵。

”

与非网原创内容,谢绝转载!

系列汇总:

之一:温故而知新:从电路里来,到Verilog里去!

之二:Verilog编程无法一蹴而就,语言层次讲究“名正则言顺”

之三:数字逻辑不容小窥,电路门一统江湖

verilog传奇 相关文章:

- Windows CE 进程、线程和内存管理(11-09)

- RedHatLinux新手入门教程(5)(11-12)

- uClinux介绍(11-09)

- openwebmailV1.60安装教学(11-12)

- Linux嵌入式系统开发平台选型探讨(11-09)

- Windows CE 进程、线程和内存管理(二)(11-09)