Verilog语言:还真的是人格分裂的语言

3’b000:3比特宽度全0; 3’b0?0:3比特宽度第二比特不关心,其他比特为0; 3’b00z:3比特宽度最低比特为不关心,其他比特为0 | |||

可综合性 | 可综合 | 依赖综合软件 | 依赖综合软件 |

case括弧内的变量称为控制表达式,case分支项中的常数称为分支表达式。控制表达式通常表示为控制信号的某些位,分支表达式则用这些控制信号的具体状态值来表示,因此分支表达式又可以称为常量表达式。当控制表达式的值与分支表达式的值相等时,就执行分支表达式后面的语句。如果所有的分支表达式的值都没有与控制表达式的值相匹配的,就执行default后面的语句。

default项可有可无,一个case语句里只能有一个default项。 当分支表达式可以覆盖控制表达式全部分枝路径时,default可以不写。但是,有时候这个全覆盖不是那么容易看出来的,所以建议最好写上default,哪怕有冗余这个default永远不可能被实现。也请大家放心,这种冗余综合软件会大伙儿去掉的,不必担心浪费电路资源。

每一个case分项的分支表达式的值必须互不相同,否则就会出现矛盾现象(对表达式的同一个值,有多种执行方案)。

执行完case分项后的语句,则跳出该case语句结构,终止case语句的执行。(精通C语言的大虾们请特别注意这点,这里case操作执行完之后不必写break了。)

在用case语句表达式进行比较的过程中,只有当信号的对应位的值能明确进行比较时,比较才能成功,因此要详细说明case分项的分支表达式的值。

case语句的所有表达式的值的位宽必须相等,只有这样控制表达式和分支表达式才能进行对应位的比较。一个经常犯的错误是用bx、bz 来替代nbx、nbz,这样写是不对的,因为信号x、z的缺省宽度是机器的字节宽度,通常是32位(此处 n 是case控制表达式的位宽)。

当分支表达式不完全覆盖控制表达式全部分枝路径时,您老有偷懒没有写default的情况下,可能产生时序逻辑的锁存器的,这点和条件if语句类似。例4是一个例子,说明了default的重要性。但是,图1中的“ld”是锁存器已经是时序电路的元件了,超越了本章的范围。

case语句条件覆盖不全产生会综合出锁存器

代码1:组合逻辑电路写法

module case_full

(

input[7:0] number,

input[1:0] select,

output reg[7:0] result

);

//Load other module(s)

//Definition for Variables in the module

//Logical

always @(*)

begin

case (select)

2b00:

begin

result = number + 8b0000_0001;

end

2b01:

begin

result = number;

end

2b10:

begin

result = number - 8b0000_0001;

end

default:

begin

result = 8b0000_0000;

end

endcase

end

endmodule

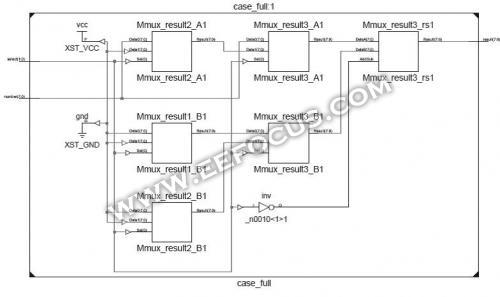

图1例4综合出的电路图(全部为组合逻辑)

4. 多路选择,一个例子

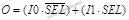

数据选择器(也称为:多路复用器,英文:multiplexer,简写:MUX),是一种从多路输入信号中选择一个信号作为输出的器件。电器符号如图2所示。

图2数据选择器的电气符号

数据选择器的的逻辑功能是:

注意,其中输入I0、I1和SEL以及输出O都是1比特位宽的信号。对应布尔逻辑表达式是

对应Verilog代码为:

1) 利用? :表达式

input SEL;

input I0;

input I1;

output O

assign O =(SEL) ? (I0) : (I1);

代码中关键的部分是? :表达式,其语法结构为 (逻辑表达式) ? (值0) : (值1);作用是

所以,以上代码满足了数字电路里面数据选择器的功能。

2) 利用if关键词

If (SEL == 1’b0)

begin

O = I0;

end

else

begin

O = I1;

end

3) 利用case关键词

case (SEL)

1’b0:

begin

O = I0;

end

1’b1:

begin

O = I1;

end

endcase

在很多情况下,需要选择的输入位宽大于1,这个时候只要两个待选择的输入与输出的位宽一致,照样可以实现功能(以下按照8比特输入为例)。此时Verilog代码除了模块的接口位宽,其他部分几乎没有变化:

input SEL;

input[7:0] I0;

input[7:0] I1;

output[7:0] O

assign O =(SEL) ? (I0) : (I1);

当然用if或者case语句也可以实现,相信读者举一反三的能力,就不罗列了。

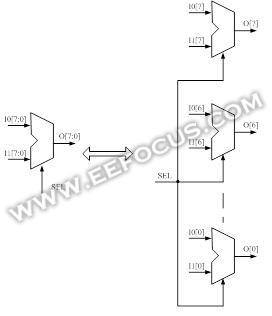

很多读者或许会感觉到笔者十分啰嗦,实则不然,图3是多位输入的数据选择器的电气原理图。

图3 多位数据选择器的电路原理图

上图看起来是顺理成章的。这里之所以笔者还不厌其烦的画出来,是为了叫读者看到多位与1比特实现上的区别。如果眼睛还没有贵恙的话,可以看出来多位数据选择器就是若干1比特数据选择器的并行排列。考虑到前面内容介绍的时延问题,需要提醒读者注意的是这个位数很高(当然不

verilog传奇 相关文章:

- Windows CE 进程、线程和内存管理(11-09)

- RedHatLinux新手入门教程(5)(11-12)

- uClinux介绍(11-09)

- openwebmailV1.60安装教学(11-12)

- Linux嵌入式系统开发平台选型探讨(11-09)

- Windows CE 进程、线程和内存管理(二)(11-09)