如何有效防止FPGA设计被克隆?

据估计,目前盛行的假冒电子产品已经占到整个市场份额的10%,这一数据得到了美国反灰色市场和反假冒联盟(AGMA)的支持。AGMA是由惠普、思科和其它顶级电子OEM公司组成的一个行业组织。据该组织估计,制造商因盗版造成的损失超过1000亿美元,而对最终用户来说,信誉损毁和可靠性问题带来的隐性成本则更难以确定。

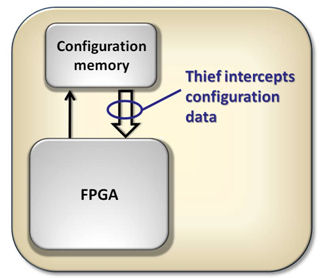

可编程逻辑的流行和ASIC的衰退带来的负面影响是拷贝设计越来越容易。对ASIC做反向工程是一件困难、昂贵且费时的工作,而拷贝最流行的FPGA配置比特流则相对简单。如图1所示。

图1:偷窃一个FPGA设计并不复杂。

因此,许多公司也许会发现他们的知识产权(IP)第二天就出现在竞争对手的产品中。剽窃者无需花费研发成本,因而能够以比合法供应商低得多的价格出售产品,从而窃取更多的市场份额。

关键问题是如何才能阻止这种偷窃行为并证明设计所有权。Algotronix公司推出的DesignTag产品试图解决上述问题。DesignTag代码可隐藏在FPGA比特流中,因此很难被定位和去除,即使剽窃者知道FPGA比特流中包含的DesignTag代码。

一旦这个代码被复制进盗版比特流中,它就像信标一样不断提示:该设计是盗版的。这在概念上非常类似于使用UV笔标记邮政编码或邮递区号,尽管它不能阻止盗版,但日后被使用时则能明确所有权。

在XC3S2000 FPGA中DesignTag代码只占用价值0.57美分的硅片(使用100片以上的目录价),占用芯片上1.3%的逻辑资源。与非法拷贝造成的潜在损失相比,这点开销微不足道。

更隐匿的问题来自所谓的“过制造(over-building)”。造成这个问题的背景是,过去10多年中许多公司撤消生产部门,专注于设计产品,并将产品交给合同厂商(CEM)制造。这种方式将CEM置于中心和关键位置。当然,绝大多数CEM是负责任的,提供有价值的服务。但也有少数不道德的CEM会生产超出合同数量的产品并出售给灰色市场,以便从中赢取超额利润。这时DesignTag就能派上用场,用来识别设计的来源和所有者。

DesignTag的另一个应用是提供串行序列号或版本识别。例如,医疗、汽车、工业、军事或航空领域的制造商可能希望在设备上打上最终用户代码的标记,或跟踪FPGA配置版本。在更新频繁的应用场合,版本控制尤其重要。无需进行电气连接就能在运作中的系统中检测出DesignTag,这对球栅阵列封装来说好处更大,因为接触这种封装的顶部要比电气连接方便得多,而且无需借助于可能影响正常工作的软件或硬件中断就能实现监视功能。

另外一个潜在的好处是让嵌入式系统与DesignTag交互,以便标记出故障或状态条件。在这类应用场合,DesignTag经过编程可以输出一个指示内部状态的不同代码。

DesignTag工作原理

DesignTag是一个小型低成本IP内核,可以内置在FPGA中作为设计的一部分。它是一种带唯一代码(“签名”)的数字内核,可以从外部识别,而无需读取FPGA比特流或内部寄存器。

它的工作原理是以一种预先定义好的方式调制主器件的功耗。微小的热脉冲能以很低的衰耗透过芯片封装传播。功率“浪涌”电平被选中以提供只有约0.1℃的封装温升。额外增加的典型功耗值是5mW,而中等规模的Spartan FPGA的正常功耗通常大于150mW,这意味着这个标记信号远低于噪声电平。

DesignTag默认情况下在工作15分钟后关闭(用户可修改这个时间),这样做有两个作用。首先,它消除了少量增加的功耗。其次,它使剽窃者的检测更加困难。DesignTag也可以被FPGA中发生的内部事件触发,这种事件可以是发送ID代码或指示内部状态,或是故障条件的一条指令。

DesignTag数据库

所有DesignTag的代码数据都保存在中央数据库中。用户可以选择将他们的代码“公开”或“隐蔽”。公开列表的优势在于所有DesignTag阅读软件都可以检测这些代码,从而允许用户、执行代理或合同厂商确认被测器件(DUT)的有效性。

相比之下,当用户不希望任何第三方知道他们的产品是否被打上了标记时,隐蔽代码是最好的选择。在这种情况下,代码由用户分发到受信任方,只有安装了这些代码的阅读软件才能检测出相应的标记。

将DesignTag集成进FPGA

在FPGA中使用的这种IP内核被实例化为HDL代码,形成一个用Verilog或VHDL编写的“黑盒”。可供交付的内容包括,用于驱动热量输出的内置代码以及电路要求的I/O引脚。全数字设计的尺寸很小,一般在赛灵思的Spartan 3 FPGA中只占用256个片(slice)。

基于安全性考虑,这种内核只提供加密过的EDIF网表。该IP采用了多种技术来阻止“反向工程”,并且能够将自己隐蔽起来防止受到篡改或检测。DesignTag内核很大程度上独立于用户设计,因此对设计流程的影响很小。

- Reed Solomon编解码器的可编程逻辑实现(06-21)

- 可编程逻辑技术在数字信号处理系统中的应用(03-09)

- 可编程逻辑器件设计技巧(06-06)

- FPGA开发板快速教程(二)(06-06)

- 基于Virtex 系列FPGA的可编程嵌入式信号处理背板的开发设计(06-06)

- CPLD/FPGA技术及电子设计自动化(06-06)