FPGA开发板快速教程(二)

时间:06-06

来源:互联网

点击:

第二章 FPGA基本教程

第一节 FPGA的基本开发流程

PLD是可编程逻辑器件(Programable Logic Device)的简称,FPGA是现场可编程门阵列(Field Programable Gate Array)的简称,两者的功能基本相同,只是实现原理略有不同,所以我们有时可以忽略这两者的区别,统称为可编程逻辑器件或PLD/FPGA。

PLD是电子设计领域中最具活力和发展前途的一项技术,它的影响丝毫不亚于70年代单片机的发明和使用。

PLD能做什么呢?可以毫不夸张的讲,PLD能完成任何数字器件的功能,上至高性能CPU,下至简单的74电路,都可以用PLD来实现。PLD如同一张白纸或是一堆积木,工程师可以通过传统的原理图输入法,或是硬件描述语言自由的设计一个数字系统。通过软件仿真,我们可以事先验证设计的正确性。在PCB完成以后,还可以利用PLD的在线修改能力,随时修改设计而不必改动硬件电路。使用PLD来开发数字电路,可以大大缩短设计时间,减少PCB面积,提高系统的可靠性。 PLD的这些优点使得PLD技术在90年代以后得到飞速的发展,同时也大大推动了EDA软件和硬件描述语言(HDL)的进步。

如何使用PLD呢?其实PLD的使用很简单,学习PLD比学习单片机要简单的多,有数字电路基础,会使用计算机,就可以进行PLD的开发。

开发PLD需要了解两个部分:1.PLD开发软件 2.PLD本身

由于PLD软件已经发展的相当完善,用户甚至可以不用详细了解PLD的内部结构,也可以用自己熟悉的方法:如原理图输入或HDL语言来完成相当优秀的PLD设计。所以对初学者,首先应了解PLD开发软件和开发流程。了解PLD的内部结构,将有助于提高我们设计的效率和可靠性。

下面我们以基于Altera公司的QuantusII软件来简单说明一下FPGA的开发流程。

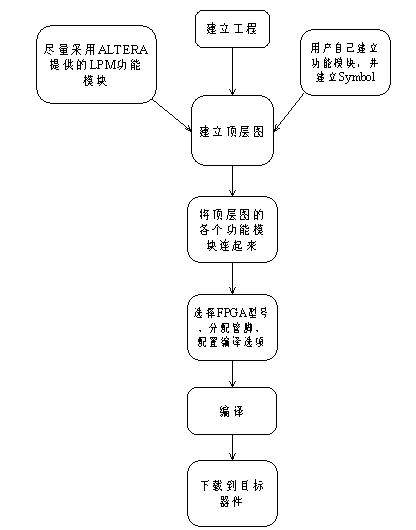

下图是一个典型的基于QuantusII的FPGA开发流程。

(2)建立顶层图。可以这样理解,顶层图是一个容器,将整个工程的各个模块包容在里面,编译的时候就将这些模块整合在一起。也可以理解为它是一个大元件,包含各个模块,编译的时候就是生成一个这样的大元件。

(3)采用ALTERA公司提供的LPM功能模块。Q2软件环境里包含了大量的常用功能模块,例如计数器、累加器、比较器、译码器等等;如果不懂得在工程中采用这些现有的功能模块真是太浪费了。以本人的经验,一个设计中一般只有极少部分的模块需要自己从零设计。

(4)自己建立功能模块。当然,有些设计中现有的模块功能不能满足具体设计的要求,那就只能自己设计啦。可以用硬件描述语言也可以用原理图的输入方法。可以把它们独立地当作一个工程来设计,并生成模块符号(Symbol),然后在顶层图中使用这个模块的符号,并将源文件(实现该模块的原理图或HDL文件)拷到顶层图所在的工程目录下。这个过程好比你要做一个电路,现在市面上没有你想要的某个芯片,你就只能自己做一块这样的一块芯片,然后添加到你的电路板上。

(5)将顶层图的各个功能模块用连线连起来。这个过程类似电路图设计,把各个芯片连接起来,组成电路系统。

(6)系统的功能原理图至此已经基本出炉了,下一步要为该设计选择芯片载体,才能真正在物理上实现系统的功能。这一步的主要工作是:(1)选择芯片型号;(2)为顶层图的各个输入输出信号分配芯片的管脚;(3)设置编译选项,目的是让编译器知道更多的信息。

(7)编译。这个过程类似软件开发里的编译,但实际上这个过程比软件的编译要复杂得多,因为它毕竟最终要实现硬件里的物理结构,包含了优化逻辑的组合、综合逻辑以及布线等步骤。在类似Q2这样的集成环境里面,这些过程都可以一气呵成,集成环境帮你自动完成了几个步骤的工作。当然,你也可以用其它工具来实现各个步骤的工作,这些内容超出了本教程陈述的范围。

(8)编译后会生成*.sof或*.pof文件,前者可以通过JTAG下载到FPGA内部,设计无误的话即能实现预期的功能,但断电后FPGA里的这些信息会丢失;后者可以下载到FPGA的配置芯片(EEPROM或FLASH芯片),掉电后这些配置信息不会丢失,重新上电以后通过该配置芯片对FPGA的内部RAM进行配置。

(9)对于复杂的设计,工程编译了以后可以采用Q2的仿真功能或其它仿真软件(如ModelSim)对设计反复进行仿真和验证,直到满足要求。

第二节 基于QuartusII的实例

实验一 实验板上的KEY1按钮控制FPGA核心板上的第一个LED灯。

本实验比较简单,使用本站FPGA开发板或者CPLD开发板以及其它FPGA开发板都可进行实验。

目的:通过该实例学习,可以了解FPGA的基本开发流程,熟识quartusII软件基本功能的使用。

原理:利用一个常开按钮(实验板上的KEY1)作为输入(常开时输入1,闭合时输入0),经过一个反相器后输出到核心板的第一个LED。KEY1常开时,LED亮,按下(闭合)实验板上的KEY1,该LED熄灭。

第一节 FPGA的基本开发流程

PLD是可编程逻辑器件(Programable Logic Device)的简称,FPGA是现场可编程门阵列(Field Programable Gate Array)的简称,两者的功能基本相同,只是实现原理略有不同,所以我们有时可以忽略这两者的区别,统称为可编程逻辑器件或PLD/FPGA。

PLD是电子设计领域中最具活力和发展前途的一项技术,它的影响丝毫不亚于70年代单片机的发明和使用。

PLD能做什么呢?可以毫不夸张的讲,PLD能完成任何数字器件的功能,上至高性能CPU,下至简单的74电路,都可以用PLD来实现。PLD如同一张白纸或是一堆积木,工程师可以通过传统的原理图输入法,或是硬件描述语言自由的设计一个数字系统。通过软件仿真,我们可以事先验证设计的正确性。在PCB完成以后,还可以利用PLD的在线修改能力,随时修改设计而不必改动硬件电路。使用PLD来开发数字电路,可以大大缩短设计时间,减少PCB面积,提高系统的可靠性。 PLD的这些优点使得PLD技术在90年代以后得到飞速的发展,同时也大大推动了EDA软件和硬件描述语言(HDL)的进步。

如何使用PLD呢?其实PLD的使用很简单,学习PLD比学习单片机要简单的多,有数字电路基础,会使用计算机,就可以进行PLD的开发。

开发PLD需要了解两个部分:1.PLD开发软件 2.PLD本身

由于PLD软件已经发展的相当完善,用户甚至可以不用详细了解PLD的内部结构,也可以用自己熟悉的方法:如原理图输入或HDL语言来完成相当优秀的PLD设计。所以对初学者,首先应了解PLD开发软件和开发流程。了解PLD的内部结构,将有助于提高我们设计的效率和可靠性。

下面我们以基于Altera公司的QuantusII软件来简单说明一下FPGA的开发流程。

下图是一个典型的基于QuantusII的FPGA开发流程。

(2)建立顶层图。可以这样理解,顶层图是一个容器,将整个工程的各个模块包容在里面,编译的时候就将这些模块整合在一起。也可以理解为它是一个大元件,包含各个模块,编译的时候就是生成一个这样的大元件。

(3)采用ALTERA公司提供的LPM功能模块。Q2软件环境里包含了大量的常用功能模块,例如计数器、累加器、比较器、译码器等等;如果不懂得在工程中采用这些现有的功能模块真是太浪费了。以本人的经验,一个设计中一般只有极少部分的模块需要自己从零设计。

(4)自己建立功能模块。当然,有些设计中现有的模块功能不能满足具体设计的要求,那就只能自己设计啦。可以用硬件描述语言也可以用原理图的输入方法。可以把它们独立地当作一个工程来设计,并生成模块符号(Symbol),然后在顶层图中使用这个模块的符号,并将源文件(实现该模块的原理图或HDL文件)拷到顶层图所在的工程目录下。这个过程好比你要做一个电路,现在市面上没有你想要的某个芯片,你就只能自己做一块这样的一块芯片,然后添加到你的电路板上。

(5)将顶层图的各个功能模块用连线连起来。这个过程类似电路图设计,把各个芯片连接起来,组成电路系统。

(6)系统的功能原理图至此已经基本出炉了,下一步要为该设计选择芯片载体,才能真正在物理上实现系统的功能。这一步的主要工作是:(1)选择芯片型号;(2)为顶层图的各个输入输出信号分配芯片的管脚;(3)设置编译选项,目的是让编译器知道更多的信息。

(7)编译。这个过程类似软件开发里的编译,但实际上这个过程比软件的编译要复杂得多,因为它毕竟最终要实现硬件里的物理结构,包含了优化逻辑的组合、综合逻辑以及布线等步骤。在类似Q2这样的集成环境里面,这些过程都可以一气呵成,集成环境帮你自动完成了几个步骤的工作。当然,你也可以用其它工具来实现各个步骤的工作,这些内容超出了本教程陈述的范围。

(8)编译后会生成*.sof或*.pof文件,前者可以通过JTAG下载到FPGA内部,设计无误的话即能实现预期的功能,但断电后FPGA里的这些信息会丢失;后者可以下载到FPGA的配置芯片(EEPROM或FLASH芯片),掉电后这些配置信息不会丢失,重新上电以后通过该配置芯片对FPGA的内部RAM进行配置。

(9)对于复杂的设计,工程编译了以后可以采用Q2的仿真功能或其它仿真软件(如ModelSim)对设计反复进行仿真和验证,直到满足要求。

第二节 基于QuartusII的实例

实验一 实验板上的KEY1按钮控制FPGA核心板上的第一个LED灯。

本实验比较简单,使用本站FPGA开发板或者CPLD开发板以及其它FPGA开发板都可进行实验。

目的:通过该实例学习,可以了解FPGA的基本开发流程,熟识quartusII软件基本功能的使用。

原理:利用一个常开按钮(实验板上的KEY1)作为输入(常开时输入1,闭合时输入0),经过一个反相器后输出到核心板的第一个LED。KEY1常开时,LED亮,按下(闭合)实验板上的KEY1,该LED熄灭。

- 用CPLD实现DSP与PLX9054之间的连接(07-23)

- 用CPLD实现FIR数字滤波器的设计(08-07)

- 基于DSP+CPLD的交流电机调速在水处理控制中的应用(11-27)

- 一种基于DSP的张力、深度、速度测量系统(04-15)

- 用双端口RAM实现与PCI总线接口的数据通讯(05-06)

- 基于DSP和CPLD的宽带信号源的设计(07-26)