FPGA开发板快速教程(二)

时间:06-06

来源:互联网

点击:

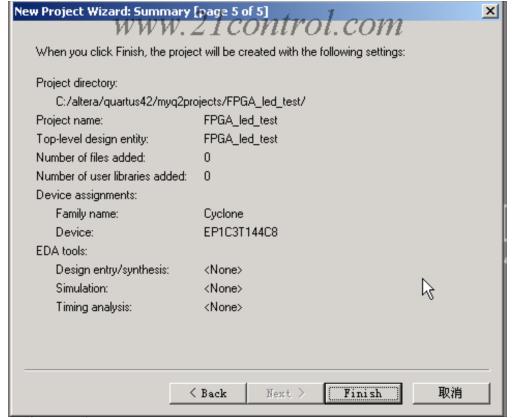

1. 建立工程

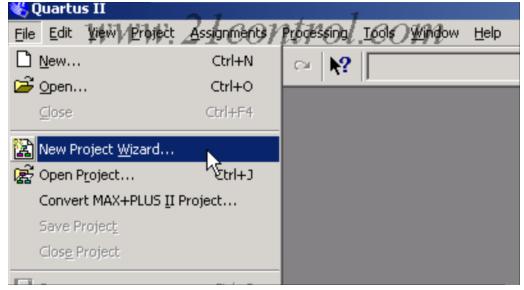

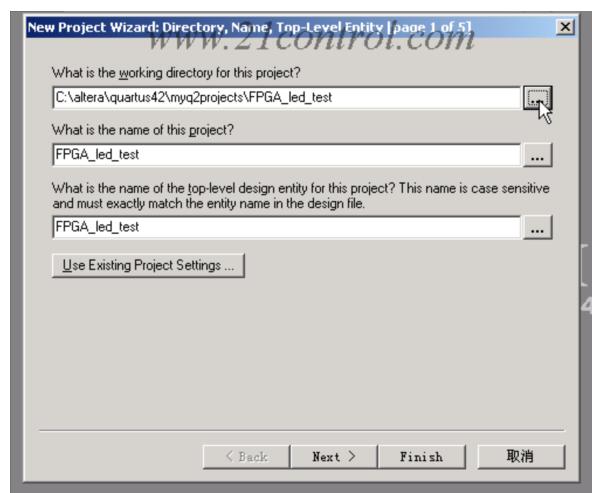

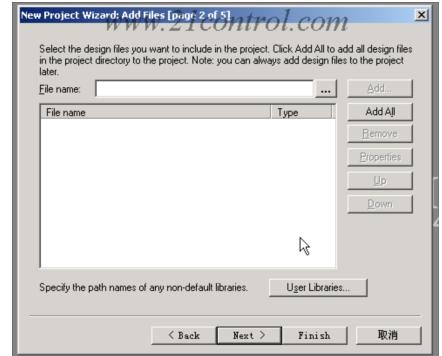

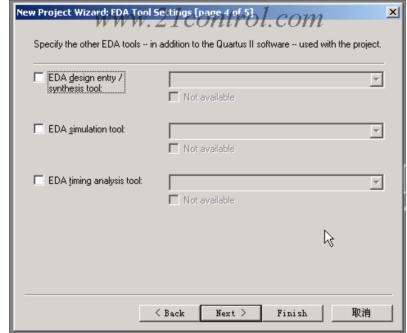

运行QuatrusII软件(以下简称Q2),建立工程,FileàNew Project Wizad如

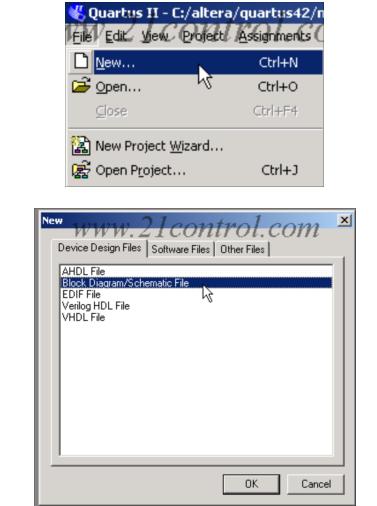

2. 建立顶层图

执行FileàNew,弹出新建文件对话框:

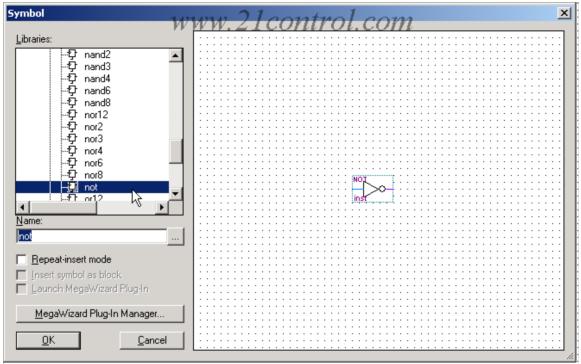

3. 添加逻辑元件(Symbol)

双击顶层图图纸的空白处,弹出添加元件的对话筐:

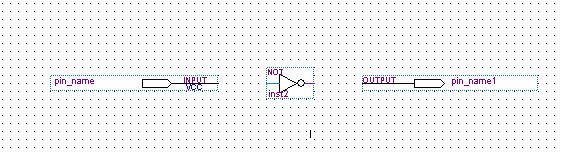

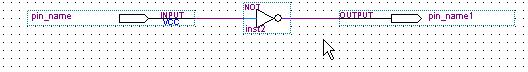

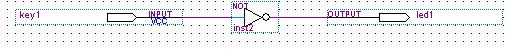

在图纸上分别添加非门(not)、输入(input)、输出(output)三个symbol,如图所示:

为芯片分配管脚可以用QuartusII软件里的“AssignmentsàPins”菜单,也可以用tcl脚本文件。用Tcl文件进行配置可重用性好,易于管理,因此本文介绍用tcl的方法。对于另一种方法,可以参考QuartusII软件的帮助文档。

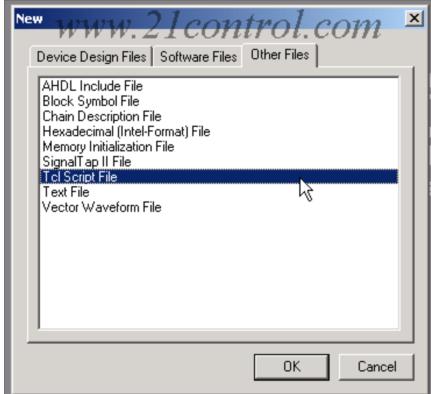

在工程目录下建立一个name为Setup.tcl的file。FileàNew,选择other files页面:

对应于EP1C6 FPGA开发板,EP1C12 FPGA开发板:

#Setup.tcl

# Setup pin setting

set_global_assignment -name RESERVE_ALL_UNUSED_PINS AS INPUT TRI-STATED

set_global_assignment -name ENABLE_INIT_DONE_OUTPUT OFF

set_location_assignment PIN_1 -to led1

set_location_assignment PIN_122 -to key1

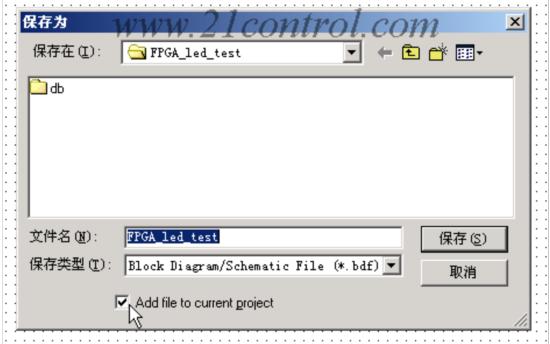

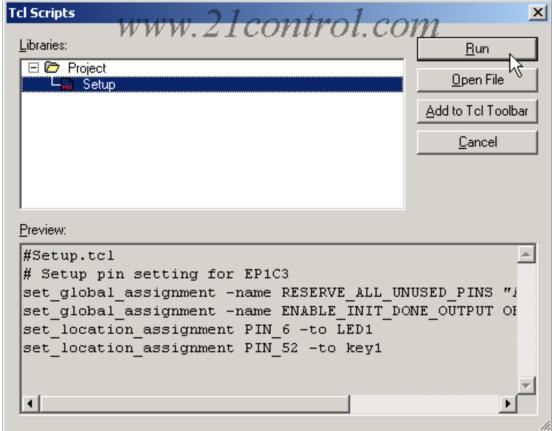

保存到工程目录下,并注意在保存对话框选上“Add file to current project”选项。然后打开Tools -> Tcl Scripts,选中刚才编辑的Script文件:Setup,并点击Run,如下图:

如果是:

C:alteraquartus51my q2projectsFPGA_led_test

在该目录下运行工程里的setup.tcl就会出错。

如果使用Tools -> Tcl Scripts 后没有弹出“tcl Script”对话框可以试一下关了QII,再重新打开。使用TCL文件分配管脚是很方便的,用户可以直接从相关例子工程中复制需要管脚分配表到自己的工程中,省时又方便。

运行QuatrusII软件(以下简称Q2),建立工程,FileàNew Project Wizad如

2. 建立顶层图

执行FileàNew,弹出新建文件对话框:

3. 添加逻辑元件(Symbol)

双击顶层图图纸的空白处,弹出添加元件的对话筐:

在图纸上分别添加非门(not)、输入(input)、输出(output)三个symbol,如图所示:

为芯片分配管脚可以用QuartusII软件里的“AssignmentsàPins”菜单,也可以用tcl脚本文件。用Tcl文件进行配置可重用性好,易于管理,因此本文介绍用tcl的方法。对于另一种方法,可以参考QuartusII软件的帮助文档。

在工程目录下建立一个name为Setup.tcl的file。FileàNew,选择other files页面:

对应于EP1C6 FPGA开发板,EP1C12 FPGA开发板:

#Setup.tcl

# Setup pin setting

set_global_assignment -name RESERVE_ALL_UNUSED_PINS AS INPUT TRI-STATED

set_global_assignment -name ENABLE_INIT_DONE_OUTPUT OFF

set_location_assignment PIN_1 -to led1

set_location_assignment PIN_122 -to key1

保存到工程目录下,并注意在保存对话框选上“Add file to current project”选项。然后打开Tools -> Tcl Scripts,选中刚才编辑的Script文件:Setup,并点击Run,如下图:

如果是:

C:alteraquartus51my q2projectsFPGA_led_test

在该目录下运行工程里的setup.tcl就会出错。

如果使用Tools -> Tcl Scripts 后没有弹出“tcl Script”对话框可以试一下关了QII,再重新打开。使用TCL文件分配管脚是很方便的,用户可以直接从相关例子工程中复制需要管脚分配表到自己的工程中,省时又方便。

- 用CPLD实现DSP与PLX9054之间的连接(07-23)

- 用CPLD实现FIR数字滤波器的设计(08-07)

- 基于DSP+CPLD的交流电机调速在水处理控制中的应用(11-27)

- 一种基于DSP的张力、深度、速度测量系统(04-15)

- 用双端口RAM实现与PCI总线接口的数据通讯(05-06)

- 基于DSP和CPLD的宽带信号源的设计(07-26)