如何有效防止FPGA设计被克隆?

图2:DesignTag提供了“偷窃证据”。

DesignTag采用2~250MHz范围之内的一个输入时钟来驱动工作时序。这个时钟应来源于系统内的任何有效时钟,而不能是专门为标记IP内核产生的时钟。最主要的原因是最低成本因素,它还能通过并入系统来迷惑检测或中止标记功能的企图。

DesignTag的控制输入可以由嵌入式系统驱动,或在设计阶段设置为默认值。例如,标记内核可以根据需要设置为连续发送;也可以在上电后的一段规定时间内发送,然后进入待机模式。还有另外一个选项,即发送序列可以在任何时间由一个触发脉冲(Trigger)输入端来启动。

标记内核可以许可最多4个不同的内置代码,这可以通过代码选择 (Code Select) 输入端进行选择。嵌入式系统可以对这个内核进行编程,让它根据要求发送其中一个代码来指示内部状态条件。例如,指示内存发生溢出或检测到软故障条件,整个过程不会中断系统功能。

篡改输出(Tamper output)信号可以从DesignTag送入嵌入式系统,这有两个好处。第一,它能用作削弱系统性能的去激活信号,并通过翻转配置比特流中的随机比特来迷惑取消标记功能的企图。第二,如果攻击者对比特流实施反向工程来重建设计,由于DesignTag块看起来像是设计的有机组成部分,因而无法被识别。

检测DesignTag输出

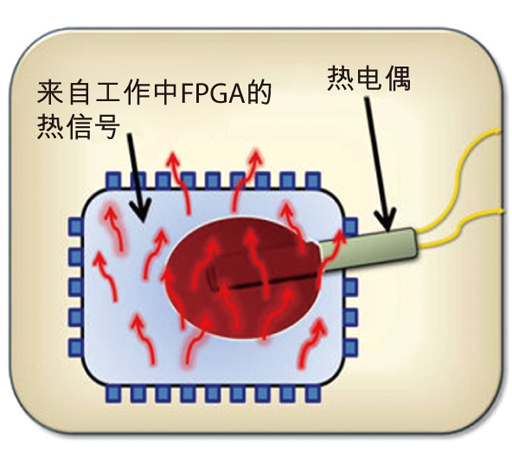

可以在器件正常工作时,将热电偶以良好热接触的方式放置在封装顶部来检测DesignTag代码,如图3所示。热量读取数据被输入进DesignTag阅读软件,并进行解密。完成代码识别的检测时间需要数分钟,系统可以检测和区分同一器件中的多个标记。

图3:用热电偶检测热信号。

不良条件可能增加检测时间,但内部算法会随着采样量的增加而使可靠性增加(图4)。如果阅读工作在静止空气中进行,获取时间则可以缩短。由于加电而导致DUT自身的散热不会阻止标记的检测。可能延长检测时间的因素包括:热不稳定状态,探针与封装之间接触不良,或一个设计中有多个代码。

图4:信号被累积和处理,直到取得很高的把握性。

DesignTag可以支持所有流行的封装类型。不过目前DesignTag不推荐用于散热器或采取强制制冷的场合。

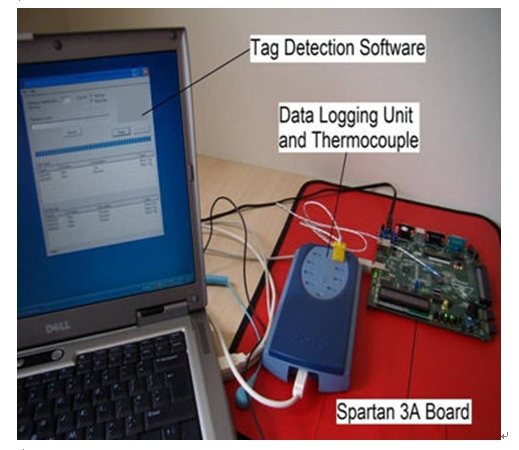

Algotronix公司推荐使用Pico科技公司带热电偶的TC-08数据记录仪。其它设备正在评估中。TC-08已包含在DesignTag入门套件中,套件中还包含有阅读器软件、安装有FPGA和5个有效DesignTag代码的评估板(图5)。阅读器软件可在运行Windows(XP或Vista)的PC上运行。

图5:入门级套件包括数据记录仪、软件、评估板和5个唯一代码。

分析攻击DesignTag的企图

任何反剽窃机制的最重要特性之一是识别、删除或去激活身份标记的难度。潜在偷窃者要解决的第一个问题是判断盗版代码中是否包含DesignTag。微小的热信号包含有64位代码,必须使用DSP和解密技术才能检测出来。扩展代码被用来控制采用线性反馈移位寄存器(LFSR)这类电路的热发生器。

扩展代码发生电路基于唯一的‘标记ID’,就像是密钥一样,其中每个密钥可导致不同的伪噪声序列。DesignTag阅读软件可以识别公开代码,但没有基础知识和授权,软件是无法检测私有代码的,这些代码将保持隐秘状态。

各种形状的标记波形是伪随机的。这些代码通过重复的功率循环和关联被观察信号能够挫败那些解码信号的企图。

另外一种可能的攻击方式是获得多个DesignTag IP内核,并在比特流或加密的网表级对它们进行比较,以便观察哪些特殊源码被修改过,并假设这些特殊源码对应的就是标记代码比特。为了挫败这种攻击,标记IP内核的许多内容以随机方式加以改变,从而在任意两个标记实例之间形成巨大数量的差异。

攻击者可能试图去激活DesignTag。DesignTag是在设计捕获阶段作为黑盒实例化进FPGA设计的,一旦融入设计,就被集成进配置SRAM器件的比特流中。用户可以选择加密这些比特流,但大多数用户不会这么做。FPGA配置比特流的大小不等,一般从中等规模的Spartan器件的2Mb到大型Virtex系列器件的10Mb都有。攻击者可能试图使用软件从比特流信息中重构网表。

虽然过去这种软件已经开发出来,并且在技术文献中有过报告,但目前攻击者似乎还无法公开得到这些工具。这种软件的输出通常是映射到FPGA原语后的扁平设计网表;虽然在比特流基础上向前进了一步,但与原始的设计源代码相比还有很大的差距。

攻击者还可能在比特流级尝试和操作设计,他们会有选择的“翻转”某些比特,然后在关闭安全特性的情况下监视效果。挫败这种攻击的关键是使每次‘翻转一个比特,然后观察发生了什么’所需的时间尽可能长,并使攻击者很难判断实际的安全特性是否完全被关闭。读一个DesignTag代码需要花数分钟时间,这使得类似这种基于研究的攻击的可行性大大降低。

与FPGA设计安全机制相比,DesignTag的优势还在于它不依赖于FPGA的特定资源,而攻击者很容易利用这种依赖性确定比特流中的位置。

基于闪存或反熔丝技术的FPGA是在工厂中配置的,因此包含DesignTag的代码不会泄漏给最终用户。针对DesignTag的任何攻击都将涉及物理性地篡改器件,从而导致FPGA损坏。

- Reed Solomon编解码器的可编程逻辑实现(06-21)

- 可编程逻辑技术在数字信号处理系统中的应用(03-09)

- 可编程逻辑器件设计技巧(06-06)

- FPGA开发板快速教程(二)(06-06)

- 基于Virtex 系列FPGA的可编程嵌入式信号处理背板的开发设计(06-06)

- CPLD/FPGA技术及电子设计自动化(06-06)