基于CPLD的电子秤逻辑接口设计

4 打印机驱动设计

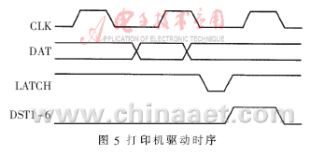

打印机是商用电子秤不可或缺的部件之一。热敏打印的原理是在控制逻辑的驱动下,通过控制打印头上排成方阵或条形式的微型发热器加热热敏纸使之产生一个与加热元素相同的图元,同时还控制进纸,以便印出整个图形(如销售商品条形码)。本文选用精工热敏打印机LTP1245,每一行384个加热点,最宽打印48mm宽带纸,打印加热电压范围4.2~8.5V,电源设计方便。为了减少打印电流,将每行分成六段,每段64点,分六次打印,其工作时序见图5。CLK是移位时钟信号,DAT是打印位数据,LATCH是数据锁存信号,DST是段控制信号。

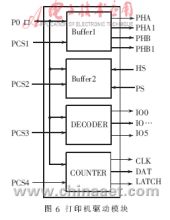

打印数据在CLK时钟控制下从串行数据线DAT脚逐位输入打印机内,而后在LATCH锁存信号控制下保存在打印存储器中。数据全部锁存到数据存储器之后,在DST1-DST6信号的控制下分6次加热打印。当某路DST信号有效时,对应段被加热打印。384个数据位恰好对应384个加热点,当该位为0时不加热,打印纸上对应位置显白色,反之纸显黑色。打印加热时间由DST的持续时间控制,持续时间可以控制打印图形对比深度。根据图5中时序,结合上述设计思想,在CPLD中抽象出功能图如图6,Buffer1缓存步进电机驱动信号,驱动打印头四相精密步进电机,Buffer2缓冲打印头过热和缺纸传感信息。Buffer1的数据从P0口写入,Buffer2的数据被P0口读入。DECODER是译码器,译出6位打印机段加热控制信号,COUNTER实际上是串并转换器,将并行打印数据转换成串行数据以及移位时钟和锁存信号。

5 仿真验证

首先,使用硬件描述语言将每个独立的单元模块抽象出硬件实体,在EDA工具软件中调试通过并生成符号模型,然后再生成包含地址分配模块和接口部件的顶层文件,仿真出波形,完成整个设计。

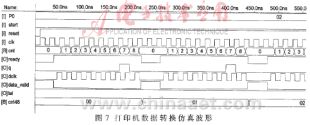

图7为将CPU输入的并行数据转换成串行数据的打印机数据并-串转换仿真波形图,在图5的时序驱动下将串行数据输入到打印机。在MAXPLUS II中选定CPLD器件,对这一部分电路做timing analyzer分析,得到理论移位时钟的最高频率可以达到111MHz。这一结果的重要意义在于:假设一个并行数据需经过8个时钟后被移入打印机中,当CPU工作在40MHz时,若其发送一个并行数据到CPLD需要4个指令周期,每个指令周期需用12个机器周期,则CPU每发送一个并行数据的无间隔时间大约为(1/40)×4×2即1.2μs。可见,只要CPLD的并-串转换模块移位时间小于1.2μs即工作频率大于0.83MHz,即可实现单片机与打印机之间的零等待时间数据传输,这对于提高打印机打印速度非常有帮助。图5显示了将一个并行数据2移位的例子,最低位(LSB)最先从右边移出。

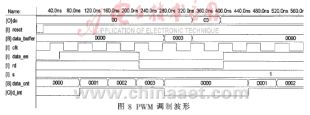

图8是PWM调制转换仿真验证波形图。PWM(Pulse Wide Moudulation)脉宽调制电路,实现将模拟信号转换成数字信号,是一种低成本高性能A/D采样方法。图中data_cnt计数器在data_en高电平信号作用下开始对clk脉冲计数,当data_en为低电平时停止计数,如果此时刚好rd也为低电平,则data_cnt被读出do数据线。很显然,这实际上是对data_en脉冲宽度计数。需要说明的一点是data_cnt为16位计数器,而CPU是8位,CPU在s控制信号的作用下分两次读出data_cnt数值。

本文论述了基于单片机和CPLD协同控制的商用电子秤设计方案,从应用角度着重研究了典型单片机应用系统中以CPLD作为逻辑控制部件的设计理念和实现方法,仿真验证了设计的正确性。其中面向存储器扩展、打印机驱动等问题的CPLD设计方法对CPU是透明的,其意义不仅在于可以提高系统的稳定性、减少CPU负荷、缩短调试周期和降低生产成本,而且可以泛化到DSP或其他类型CPU的应用系统中,因此具有推广价值。

- 针对状态机的综合优化策略(06-05)

- PLC的产生、定义、特点与分类(12-16)

- 70PR02可编程逻辑控制处理模块(12-02)

- 以FPGA为核心的逻辑控制模块的数据采集系统(10-10)

- 基于PLC的火力发电厂现地控制单元的研究(09-20)

- 基于AT89C55单片机的PLC研究(01-19)