采用EDA或FPGA实现IP保护

1 引言

随着电路规模不断扩大,以及竞争带来的上市时间的压力,越来越多的电路设计者开始利用设计良好的、经反复验证的电路功能模块来加快设计进程。这些电路功能模块被称为IP(Intellectual Property)核。IP核由相应领域的专业人员设计,并经反复验证。IP核的拥有者可通过出售IP获取利润。利用IP核,设计者只需做很少设计就可实现所需系统。基于IP核的模块化设计可缩短设计周期,提高设计质量。现场可编程门阵列FPGA具有可编程特性,用户根据特定的应用定制电路结构,因此其处理速度大大超过通用处理器。与ASIC相比,FPGA的缺点是在提供灵活的可编程同时,则以芯片的面积、功耗和速度做为代价。

近年来,单个FPGA实现电路规模不断扩大,设计者可以在单个FPGA上实现一个完整的系统(System on Pro—grammablb Chip,简称SoPC)。IP核的出现为SoPC的设计提供极大便利,利用IP核,设计者通过模块化设计。轻松快速地实现系统复杂的功能。

当设计者从第三方购买IP,需要一定的保护机制防止设计者在非授权IP核使用,以保护IP核所有者的利益。同时,对于设计者完成的设计,也需要相应的保护机制防止设计被非法复制、窃取或篡改。为此,提出一种结合电子设计自动化(Electronic Design Automation,简称EDA)软件和FPGA的IP核保护机制。通过在EDA工具中加入保护机制防止设计者非授权使用IP核,在FPGA中加入保护机制防止设计被非法复制、窃取或篡改。

2 EDA软件中实现IP保护

FPGA的设计开发流程主要包括行为综合、逻辑综合、技术映射和布局布线。一般情况,设计者使用硬件描述语言(如VHDL,Velilog)描述电路,然后由EDA软件对其处理。

在EDA软件处理流程中,行为综合把算法级或寄存器传输级(Register Transfer Level,简称RTL)的电路描述转换为门级的网表,逻辑综合优化门级网表,技术映射是将优化后的网表映射为FPGA中的具体实现(查找表),布局布线工具则按照一定的评价标准来确定最终的电路单元在FPGA中的位置,并利用连线资源实现电路单元间的连接。

如果设计者利用第三方提供的IP核实现所需的设计,为了避免设计者窃取IP核后,对其修改,并将其据为已有,需要有相应的安全机制来保护第三方设计的IP核。

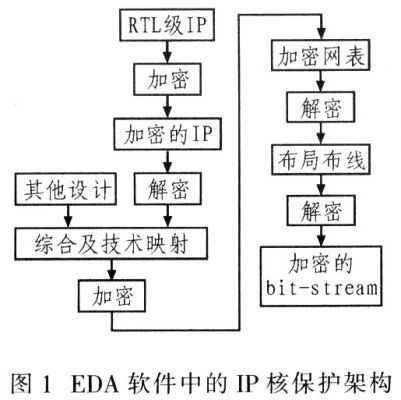

在EDA软件的处理流程中,EDA软件必须能够正确解析设计,才能完成处理,因此设计本身对于EDA软件是公开的。这里假定EDA软件是可信的。具有IP核保护机制的EDA流程如图l所示。第三方设计的IP核要先向EDA软件的开发用户购买RTL级的IP核后,第三方将该IP核先用EDA开发商的公开密钥对该IP核加密,再用设计者提供的公开密钥加密。这样,设计者虽然得到了第三方的IP核,但是并不知道EDA软件开发商的私钥,因此设计者无法知道该IP核中RTL级的描述。

设计者可将购买的IP核看作功能已知的黑盒子,在利用黑盒子和其他的电路模块完成电路描述之后,设计者将设计导入EDA工具。EDA工具分别利用设计者输入的密钥和EDA开发商的密钥对加密的IP核进行两次解密,从而得到整个设计完整的RTL表示。然后,EDA工具可以对设计进行行为综合、逻辑综合和技术映射,最后生成技术映射后的网表。假定用于综合和技术映射的工具是由某个EDA开发商提供,而FPGA布局布线工具是另外的EDA开发商,例如由FPGA的生产商提供。

在将优化后的门级网表写入文件之前,该EDA工具先用自己的私钥对网表进行加密处理,再用布局布线工具提供商的公钥对网表进行加密处理。这样设计者还是无法查看到综合和技术映射后的网表,从而防止了设计者用逆向工程的方法来窃取IP核。

布局布线工具先用自己的私钥对加密的网表进行一次解密,再用前端的EDA工具开发商的公钥进行第二次解密,从而得到解密后的网表。利用该网表,布局布线工具可以完成设计在芯片上的布局布线,最终生成用于FPGA配置的bit-stream文件。

3 FPGA中实现IP保护

在EDA软件生成了用于配置FPGA的bit-stream后,将bit-stream加载到FPGA中,就可以完成对FPGA的编程,FPGA实现设计者期望的功能。FPGA分为非易失性(Don—volatile)和易失性(volatile)两种,前者包括基于反熔丝技术和Flash技术,后者主要是基于SRAM技术。对于基于SRAM的FPGA,因为其配置信息在掉电之后就会丢失,因此一般需要用PROM存储FPGA的配置信息,以使FPGA在重新加电后能够再次根据这些信息进行配置。FPGA的配置信息就是设计在FPGA上的最终实现,因此需要相应的技术手段来保护这些配置信息。

因此FPGA的bit-stream是二进制信息,它是依赖于设计本身和具体的FPGA结构。一般来说,bit-stream的生成工具都是由FPGA的生产商提供。FPGA的生产商虽然会给出一些bit-stream生成工具的使用信息,但一般都不会公开FPGA的bit-stream编码格式。由于不知道FPGA的bit-stream文件格式,目前尚未发现对FPGA的编程bit-stream文件成功实现逆向工程,所以绝大多数的FPGA使用者都不考虑FPGA中的设计会被破解。

虽然bit-stream文件难以被逆向工程方法破解,但如果这些bit-stream被复制,利用这些bit-stream,再使用同样的FPGA,竞争对手就可以生产同样产品。也这是说,设计还是有可能被盗窃。因此,需要相应的安全机制来防止bit-stream被复制。针对基于SRAM的FPGA,下面讨论两种防范机制。

3.1 一次加载

- 嵌入式系统设计方法的演化——从单片机到单片系统(01-28)

- Proteus在单片机教学和科技制作中的应用与实践(03-02)

- FPGA 原型设计:软件最重要!(03-21)

- 电子系统设计自动化方法和设计环境的研究(07-21)

- SoC:IP是新的抽象(10-24)

- 鳍式场效晶体管寄生提取的复杂性(12-26)