基于DSP的嵌入式导航计算机系统中CPLD器件软件更新的实现

3 CPLD的JTAG接口编程的软件设计

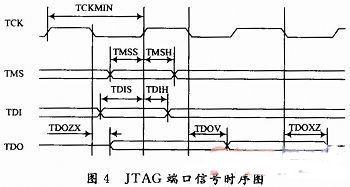

在硬件设计的基础上,为实现通过DSP的GPIO口模拟JTAG信号时序逻辑来对CPLD进行软件更新,需严格按照JTAG标准中的端口信号时序要求。对于本文所用的CPLD器件,其JTAG端口信号时序关系如图4所示。

由图4可见,对于JTAG口时序逻辑需考虑如下3项内容:

(1)JTAG接口要求一个最小时钟周期TCKMIN。

(2)JTAG接口在TCK的上升沿采样TMS和TDI信号。因此在TCK上升沿之前,TMS和TDI要具有最小分别为TMSS和TDIS的建立时间,同时在TCK下降沿之后要保持最小分别为TMSH和TDIH长的时间。

(3)在TCK的下降沿,JTAT接口输出新的TDO值,并保持至少TDOV长的时间。

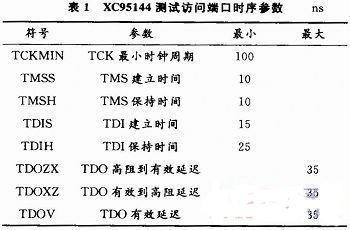

本文所用CPLD的JTAG端口时序参数要求如表1所示。

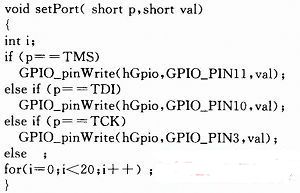

在本文设计的导航计算机系统中,DSP的工作主频为200 MHz,利用TI公司提供的库函数,由该DSP的GPIO口模拟的时钟频率最大不超过3 MHz,可以满足表中TCKMIN参数对应的最大10 MHz的要求。对于建立和保持时间等参数要求,可通过软件延时或定时器实现。由于在本系统的应用中,DSP在上电期间专注于CPLD的软件更新,所以本文将采用软件延时来实现这些参数要求,设计的JTAG口信号电平驱动函数模块代码如下:

利用上述代码,模拟实现的JTAG时钟信号频率为367.6 kHz。

DSP在配置CPLD器件时,不断从存储在SRAM里的XSVF文件中读出指令和参数,并根据不同的指令执行对应的操作。根据功能特点,XSVF文件中的指令主要包括:状态转移、指令移入、数据移入或移出和空闲等待这4类指令。状态转移指令用于控制TAP状态机进入与下条XSVF指令操作对应的状态中,在XSVF文件中,图2中的每个状态对应一个字节的编码;指令移入用于将TDI上的指令代码移入对应的指令寄存器;数据移入或移出指令可将TDI上的数据移入CPLD器件内部逻辑中,同时可以捕获从TDO上移出的数据;空闲等待指令可提供移进CPLD擦出指令或数据后等待内部逻辑成功响应需要的时间。

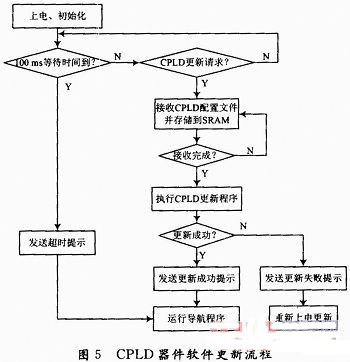

在上述设计的基础上,设计通过串行方式的CPLD更新流程如图5所示。

图5中系统首先通过DSP的串行口接收CPLD的编程配置文件,接收完配置文件后,可在35 s之内完成CPLD的软件更新。在实际应用中,应用本文的更新方案,可根据需要很快实现不同的系统配置方案,如可选择INS和GPS组合。或与地磁组合等,无需重新更改硬件,便可配合多种传感器,克服了通过常用PC机与下载线缆进行软件更新的弊端,避免了反复打开、组装系统等一系列的繁琐工作,提高了现场调试的效率,从而提高了导航计算机系统的适应性。

4 结语

通过硬件和软件设计,本文实现了基于DSP的CPLD器件软件更新的串行方式。目前已在本课题组研制的基于DSP和CPLD的嵌入式导航计算机系统中进行了成功应用。该串行口更新方式相对常用的基于PC并口的编程方法,解决了并口转JTAG口的下载线缆过长而不能可靠对CPLD更新的问题,同时可以实现CPLD器件在系统的远端更新,避免了繁琐的现场拆除板卡进行软件更新和升级的弊端,提高了系统的可维护性。另外,通过外加网络接口,应用本文设计的软件更新方案,还可实现CPLD器件的远程更新。本文的设计对于嵌入式导航计算机系统的更新和升级具有较好的适用性,提高了系统应用的灵活性,可以应用到具有不同配置的多种导航系统中,也可以在一种导航计算机系统中通过对CPLD的不同配置来适应不同的传感器和接口。

CPLD器件软件更新 DSP JTAG 相关文章:

- 在采用FPGA设计DSP系统中仿真的重要性 (06-21)

- 基于 DSP Builder的FIR滤波器的设计与实现(06-21)

- 达芬奇数字媒体片上系统的架构和Linux启动过程(06-02)

- FPGA的DSP性能揭秘(06-16)

- 用CPLD实现DSP与PLX9054之间的连接(07-23)

- DSP+FPGA结构在雷达模拟系统中的应用(01-02)