SOC时序分析中的跳变点分析

跳变点是所有重要时序分析工具中的一个重要概念。跳变点被时序分析工具用来计算设计节点上的时延与过渡值。跳变点的有些不同含义可能会被时序分析工程师忽略。而这在SoC设计后期,也就是要对时序签字时可能会导致问题。后端设计工程师要知道跳变点的概念及其含义,这个非常重要。这也正是本文目的之所在。

1.跳变点定义:

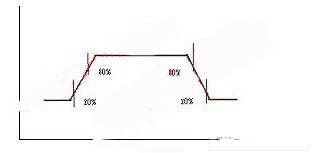

跳变点可定义为逻辑高电平的百分比,作为测量压摆率和时延值的参照。图1(a)演示的是压摆率跳变点。

图1(a)

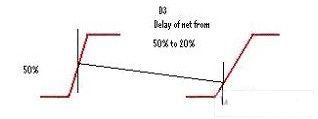

图1(b)演示的是时延跳变点。

图1(b)

跳变点用来描述标准单元或硬模块(IP)等的引脚过渡值特征,同时检查SoC时序。通常跳变点的值在时序模型(自由格式)中提及,时序分析工具在计算时延和压摆率时会使用这些值。

2.如何固定跳变点:

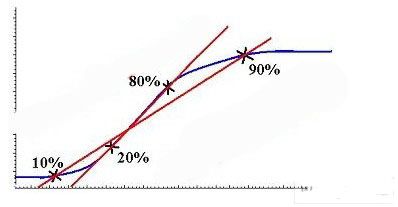

在描述标准单元或硬模块(IP)特征时,跳变点对于特定的技术节点是固定的。将跳变点固定的目的是确保测量的时延/压摆率接近实际(SPIce)的波形。如图2(a)所示,当跳变点位于切换波形的线性区(20%-80%)时,压摆率值比位于非线性区(10%-90%)时要令人乐观。

图2(a)

通常情况下,在过渡跳变点位于线性区时,时序工具计算的单元时延更接近Spice结果。

同时,晶体管的电压阈值(Vt)特性对于决定跳变点发挥了重要作用,因为输出波形在输入电压超过晶体管的Vt值后会发生线性化[1]。

时延阈值在输入和输出波形的线性区是固定的。只要时延跳变点位于波形的线性部分,那么时延跳变点是20-80还是50-50都没有关系。

3.自由格式提及的跳变点句法

下面给出的是典型时序模型(.liberty文件)的快照,以指示正在使用的跳变点

input_threshold_pct_rise:50;

input_threshold_pct_fall:50;

output_threshold_pct_rise:50;

output_threshold_pct_fall:50;

slew_lower_threshold_pct_rise:20;

slew_lower_threshold_pct_fall:20;

slew_upper_threshold_pct_rise:80;

slew_upper_threshold_pct_fall:80;

4.时序工具如何处理跳变点来计算时延

a)当跳变点对于界面都相同时:

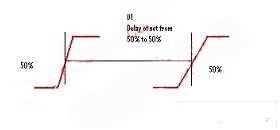

图3(a)描述了驱动程序和负载具有相同时延阈值时的情况。

在给出的示例中,两者都为50%。

图3(a)

此时,,考虑压摆率降级(由网络引起)后,时序工具计算的驱动程序达到其50%的逻辑高值和负载达到其50%的逻辑高值时两者之间的时间差。

类似的解释对于特定单元的输入和输出产生的下降信号和时延同样适用。压摆率值根据.lib中提及的变量进行计算。

b)当跳变点对于一个界面而不同时

(i)20%比50%:

图4(a)描述了驱动程序时延跳变点为20%而对负载单元跳变点为50%的情况。

在这种情况下,与负载信号相比,驱动程序的信号会快速达到其时延跳变点值。因此此类界面的网络时延会大于驱动程序也达到50%情形下的时延[图3(a)]。

图4(a)

时序工具可通过线性或非线性扩展计算网络上出现的额外时延。

(ii)50%比20%

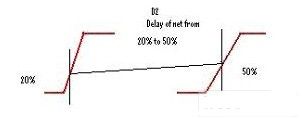

图4(b)描述了驱动程序跳变点为50%而负载单元的跳变点为20%的情形。

在这种情况下,与驱动信号相比,负载的信号会更早达到其时延跳变点值。这种情况通过时序工具借助扩展(线性或非线性)来进行处理。

图4(b)

这里需要注意的是:在这种情况下,扩展会引起“负时延”。

应注意:尽管现实世界不能在时域中后向穿越,但是时序工具需要将这种时延考虑在内,这样,从开始点(在本例中为驱动单元的输入引脚)到终端点(在本例中为负载单元的输出引脚)的整体路径时延接近现实世界时延(Spice)。

5.与跳变点相关的其他问题:

(i)SDF中的负时延:在通过时序工具完成扩展后产生的负时延将以标准时延格式(SDF)进行复制,用于门级模拟。不希望发生这种情况,因为门级模拟器无法处理负时延。

它们要么标志错误消息要么表示此类情况的零时延。作为一种变通方法,可编写一个脚本(附录A),根据所计算的负时延,增加(或减少)负载单元(或驱动单元)时延。

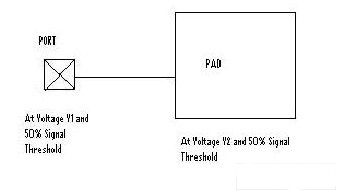

(ii)端口和IO单元之间的附加时延:

通常时序工具报告端口到I/O单元的时延。在硅片上,该网络作为接合线出现在芯片外部。因此,对于该网络物理信息不能进行量化。

时序工具提供此类网络的时延报告。原因包括:

a)由于没有时序模型可用于端口,因此时序工具采用用户定义的或默认跳变点和电压电平计算时延。

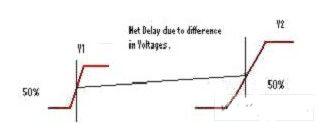

b)由于假定跳变点和端口w.r.TI/O单元跳变点的电压电平值之间有差额。图5(a)和图5(b)描述了此类情况。

图5(a)

图5(b)

要克服这种情况,可执行以下操作:

1)为与I/O单元的端口相同的端口定义运行条件。

2)编写脚本为此类网注释零时延。

(iii)带有丢失跳变点的库

如果我们拥有不包含跳变点阈值或电压电平值的时序模型,那么来自/到此类模型的界面的时延可能不正确。因为时序工具使用跳变点和电压电平的默认值,分析这些路径。作为一种变通方法,用户应在向负责库的人员进行咨询后,再定义跳变点。

- FPGA设计者需要练好5项基本功(06-05)

- SPI总线小结(12-15)

- 单片机时序分析(04-10)

- I2C总线信号时序分析(07-20)

- 短波通信中一种时延设计方法与DSP实现(05-02)

- FPGA设计系统时钟的影响因素及其分析(06-05)