SPI总线小结

SPI接口是在CPU和外围低速器件之间进行同步串行数据传输,在主器件的移位脉冲下,数据按位传输,高位在前,地位在后,为全双工通信,数据传输速度总体来说比I2C总线要快,速度可达到几Mbps。

1、SPI总线主要特点

· 全双工;

· 可以当作主机或从机工作;

· 提供频率可编程时钟;

· 发送结束中断标志;

· 写冲突保护;

2、接口定义

该总线通信基于主-从配置。它有以下4个信号:

MOSI:Master Out Slave In主出/从入

MISO:Master In Slave Out 主入/从出

SCK:Serial Clock 串行时钟

SS:Slave Select 从属选择

芯片上“从属选择”(slave-select)的引脚数决定了可连到总线上的器件数量。

3、SPI时序分析

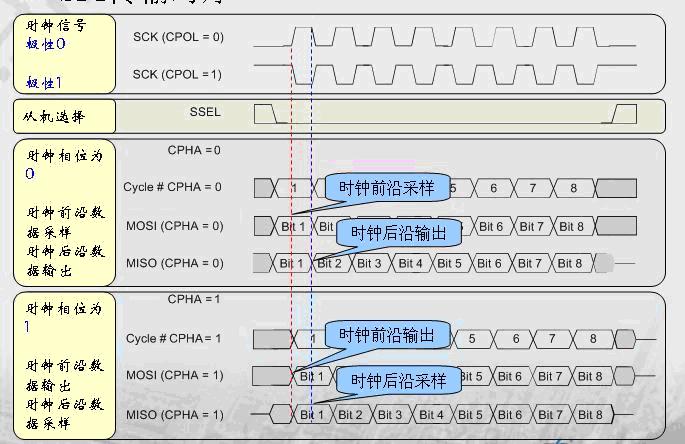

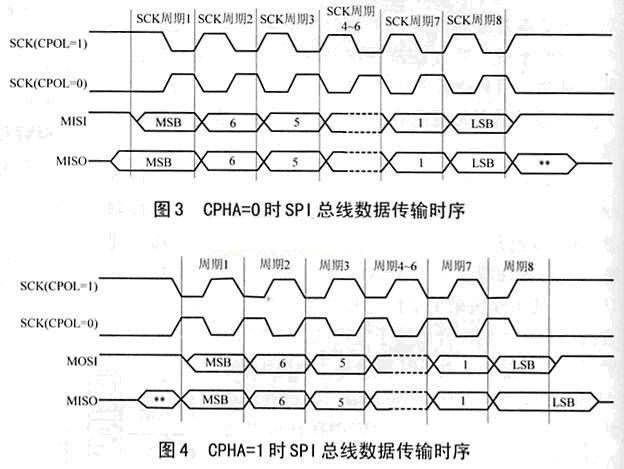

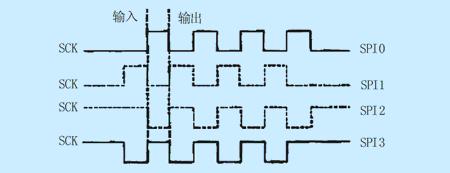

在SPI传输中,数据是同步进行发送和接收的。数据传输的时钟基于来自主处理器的时钟脉冲,摩托罗拉没有定义任何通用SPI的时钟规范。然而,最常用的时钟设置基于时钟极性(CPOL)和时钟相位(CPHA)两个参数,CPOL定义SPI串行时钟的活动状态,而CPHA定义相对于SO-数据位的时钟相位。 CPOL和CPHA的设置决定了数据取样的时钟沿。如图1所示,根据CPOL和CPHA的不同,有四种不同的工作模式。

其中,CPOL是用来决定SCK时钟信号空闲时的电平。CPOL=0,空闲电平为低电平,CPOL=1时,空闲电平为高电平。CPHA用来决定采样时刻的,CPHA=0,在每个周期的第一个时钟沿采样。CPHA=1,在每个周期的第二个时钟沿采样。

关于时序分析,网上有几张流行的说明图表,意义是相同的。

图2 SPI时序分析

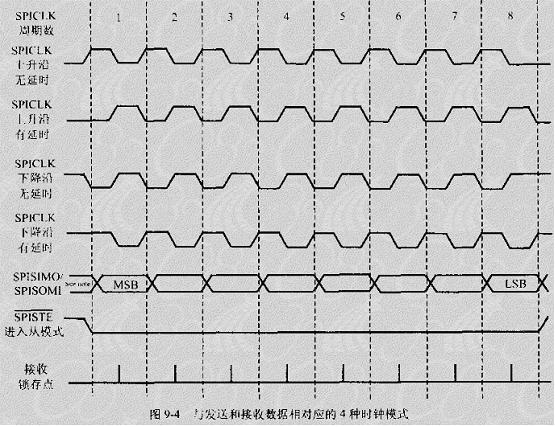

图4 SPI时序分析

虽然表述的侧重点不同,但描述的意思是一致的。根据SCK无效电平和采样时刻的不同,2x2=4种时序。

4、注意事项

1)在Mcbsp的手册中,SPI的时序表述有所不同。SCK无效电平表述是相同的,但是采样时刻的表述她是通过有无delay来表达的。对比如下:

CPHA = 0表示在每个周期的第一个时钟沿采样,对应存在delay;

CPHA = 1表示在每个周期的第二个时钟沿采样,对应无delay。

2)在不同场合下,发送和接收的表述词汇可能不同。比如:

发送可表述为:transmit,output

接收可表述为receive,sample,latch

3)SPI主模块和从设备时钟相位和极性应该一致。个人理解这句话有2层意思:其一,主设备SPI时钟和极性的配置应该由外设来决定,也就是说主设备这边的时钟极性和相位都是以从设备为基准的;其二,两者的配置应该保持一致。

SPI总线时序分析串行外围接 相关文章:

- Windows CE 进程、线程和内存管理(11-09)

- RedHatLinux新手入门教程(5)(11-12)

- uClinux介绍(11-09)

- openwebmailV1.60安装教学(11-12)

- Linux嵌入式系统开发平台选型探讨(11-09)

- Windows CE 进程、线程和内存管理(二)(11-09)