码长可变、纠错能力可调的RS码编码器设计

个复位信号。编码后便可得到码字为(m 8, …, m 0, D 3, …, D 0 )。RS(15, 9) 码编码电路的求余运算要6 级的移位寄存器来实现。因此K 开通, add5 的输入端接D5 的输出端。

在编码电路中乘法器采用了基于多项式乘法理论GF (2m ) 上的m 位有限域乘法的方法, 大大地提高了电路的运算速度。

快速有限域乘法器实现:

快速有限域乘法的实现思路如下, 以RS (7, 3)码为例:

因此就可以实现快速有限域乘法器, 这样对电路的运算速度将会有很大的提高。由于RS (15,11) 码和RS (15, 9) 码基于同一个有限域GF (24 ) ,因此它们的乘法器一样。当sel 置为01 时, 乘法器工作在GF (23 ) 的乘法状态, 当sel 置为10 或11时, 乘法器工作在GF (24) 的乘法状态。只不过工作在GF (23 ) 状态时乘法器输入输出端的第4 位为0。

电路仿真及测试

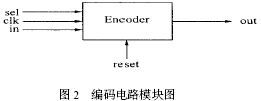

编码电路模块可以表示为:

sel 是编码电路的选择端, clk 是时钟输入端,reset 是系统复位端, in 是信息输入端, ou t 是码字输出端。

用V erilog HDL 语言编写电路的代码后, 再用Cadence 公司的NC V erilog HDL 仿真工具进行仿真, 得到各种编码的仿真结果。

A ) 给reset 一个复位信号, 使电路处于零状态, sel 置为01 时, 输入信息电路开始编码。输入信息位为(0, 1, 2) , 编码后得到校验位(2, 3, 1, 3) , 因此输出端输出码字为(0, 1, 2, 2, 3, 1, 3)。然后再输入信息位, 循环进行编码。输出波形如图3 所示。

B) 给reset 一个复位信号, sel 置为10 时, 输入信息电路开始编码。输入信息为(0, 1, 2, 3, 4, 5, 6,7, 8, 9,A ) , 编码后得到校验位(C, E, 8, 3) , 所以输出端输出码字为(0, 1, 2, 3, 4, 5, 6, 7, 8, 9,A , C, E,8, 3)。输入端再次输入信息, 循环进行编码。输出波形如图4 所示。

C) 给reset 一个复位信号, sel 置为11 时, 输入信息电路开始编码。输入信息为(0, 1, 2, 3, 4, 5,6, 7, 8) , 编码后得到校验位(B, C, 0, 5, 7, 8) , 所以输出端输出码字为(0, 1, 2, 3, 4, 5, 6, 7, 8,B, C, 0,5, 7, 8)。输入端再次输入信息, 循环进行编码。

仿真完成后, 采用Xilinx 的FPGA 板, 主芯片为SPARTAN II XC2SPQ 208 进行验证, 输入信息与仿真输入的信息一致, 然后用逻辑分析仪观测输出结果。

A ) 给reset 一个复位信号后, 使电路工作在RS (7, 3) 码的编码状态。用逻辑分析仪观测输入与输出的结果如下图6 所示, 虚线圈起来的(0, 1, 2,2, 3, 1, 3) 表示一个完整的输出码字。

B) 先使电路复位, 然后让电路工作在RS (15,11) 码的编码状态, 用逻辑分析仪观测输入与输出结果如下图7 所示, 虚线圈起来的(0, 1, 2, 3, 4, 5,6, 7, 8, 9,A , C, E, 8, 3) 表示一个完整的输出码字。

C) 电路复位后, 使它工作在RS (15, 9) 码的编码状态, 用逻辑分析仪观测结果如下图8 所示, 虚线圈起来的(0, 1, 2, 3, 4, 5, 6, 7, 8,B, C, 0, 5, 7, 8)表示一个完整的输出码字。

从上面的仿真波形和测试结果可以看到他们的输出结果一致, 验证了设计的正确性。

电路参数

用Xilinx 公司的Pro ject Navigator 综合工具对电路代码进行综合后, 得到电路的等效门单元数1339; 测得电路的静态功耗为12.50 mW , 最高作频率为100MHz。

结论

提出了一种码长可变、纠错能力可调的RS 码编码器, 它解决了以往RS 编码器只能对单一码长和固定纠错能力编码的局限, 同时采用快速有限域乘法的方法提高了电路的运算速度。设计后通过在FPGA 上测试, 验证了设计的正确性。

- μC/GUI在基于NiosⅡ嵌入式开发平台的环境智能监控系统中的移植与应用(01-14)

- 基于Zynq的OLED驱动设计(10-04)

- 如何仿真IP核(06-06)

- LabVIEW FPGA代码模块设计(IP核)(06-06)

- IP核互连策略及规范(06-06)

- 如何实现IP核心网的QoS(06-06)