基于FPGA的遗传算法组合逻辑电路设计

时间:06-05

来源:互联网

点击:

3 实验结果

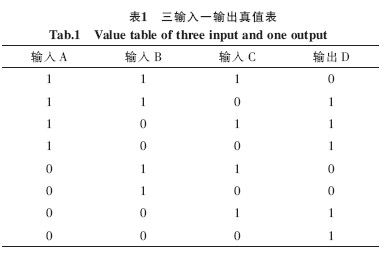

系统在Altera公司的Cyclone系列EPIC6Q240C8型号芯片上进行了实现。系统采用Verilog语言编写,开发平台为Altera公司自带的Quart usII 6.0集成环境。为验证系统的正确性和测试系统的性能,本文,对系统进行了测试,即给出一个三输入一输出的组合逻辑电路的真值表,测试真值表如表1所示。

遗传算法参数设置如下:种群规模为100,交叉概率为0.6,变异概率为0.1,基因长度为16,遗传代数为100。其中针对给出的真值表,通过代码输入、编译、综合、布局布线后,得到结果如图2所示。

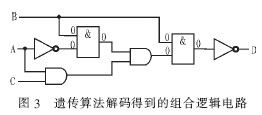

即最优解为:C3bFC396。经过解码,得到电路图如图3所示。所得到的电路图满足真值表的要求。

4 结束语

本文在FPGA上实现了基于遗传算法的组合逻辑电路的自动设计。对整个系统结构进行了自顶而下的设计,对模块功能进了划分。硬件实现遗传算法能有效地缩短运行时间,为实时应用提供了可能。随着FPGA芯片技术的进一步发展,大规模并行遗传算法的实现也将成为可能。

- 在采用FPGA设计DSP系统中仿真的重要性 (06-21)

- 基于 DSP Builder的FIR滤波器的设计与实现(06-21)

- 基于FPGA的快速并行FFT及其在空间太阳望远镜图像锁定系统中的应用(06-21)

- 3DES算法的FPGA高速实现(06-21)

- 用FPGA实现FFT算法(06-21)

- FPGA的DSP性能揭秘(06-16)