FPGA系统设计的仿真验证之: 仿真测试文件(Testbench)的设计方法

7.5仿真测试文件(Testbench)的设计方法

7.5.1测试文件的用途

随着设计量和复杂度的不断增加,数字设计验证变得越来越难,所消耗的成本也越来越高。面对这种挑战,验证工程师必须依靠相应的验证工具和方法才行。对于大型的设计,比如上百万门的设计验证,工程师必须使用一整套规范的验证工具;而对于较小的设计,使用具有HDLtestbench的仿真器是一个不错的选择。

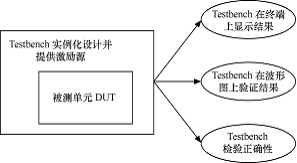

Testbench已经成为了HLL(High-Level-Language,高级语言)设计标准验证方法。一般来说,它能够完成下面一些任务。

·实例化DUT(DesignUnderTest,被测设计)。

·通过为模块添加测试向量对DUT进行仿真。

·通过终端或波形窗口提供仿真结果。

·比较实际输出与期望输出的差异。

一般来说,Testbench使用工业标准VHDL或者VerilogHDL语言来描述。简单的Testbench通过调用用户设计的功能模块,然后进行仿真。较为复杂的Testbench还包括一些其他的功能,比如包含特定的激励向量或者进行实际输出与期望输出的比较等。

如图7.32所示是一个标准的HDL验证流程,图中表达了上述的Testbench功能。

图7.32HDLTestbench仿真流程

由于Testbench是使用VHDL或者VerilogHDL编写的,因此Testbench的验证流程是跨平台的。同时由于这两种语言是标准的非私有语言,所以使用它们进行验证的流程可以在未来的设计中继续使用。

下面讲解Testbench的设计方法。

7.5.2测试文件设计方法

由于测试文件只是在仿真时使用,因此在综合中对RTL语言的语法限制在测试文件中并不存在。相反地,测试文件可以编写得更加通俗,所有的行为结构语法都可以使用,使之更加容易理解。所有的测试文件都包含了如表7.1所示的结构。

表7.1 测试文件的共同结构

VHDL | VerilogHDL |

实体和结构声明(Entity,Architecture) | 模块声明(Module) |

信号声明(Signal) | 信号生命(Signal) |

顶层模块实例化 | 顶层模块实例化 |

激励向量 | 激励向量 |

正如所述,测试文件除了包含这些共有的结构意外,还完成一些额外的工作。例如显示结果、嵌入的误码检测等。下面通过一些例子来展现测试文件中常用的结构。

1.产生测试时钟

仿真必须产生时钟才能进行,只有在推进的仿真时钟中才可以判定输出的结果是否符合设计的要求。交互时钟是硬件设计语言里面最容易实现的时钟,下面通过Verilog语言的例子来说明如何生成测试时钟。

Parameter ClockPeriod = 10; // 声明时钟周期常量

//时钟生成方法1:

initial begin

forever Clock = #(ClockPeriod / 2) ~ Clock;

end

//时钟生成方法2:

initial begin

always #(ClockPeriod / 2) Clock = ~Clock;

end

在两种实现方法中,都是用了initial块语句。在方法1中,使用了forever语句,是最常用的产生时钟的方法。在方法2中,使用过了always语句,同样也实现了时钟的生成。两种方法都产生了周期为10的时钟波形。

2.提供激励源

为了得到Testbench的验证结果,必须为DUT提供激励向量。并行激励模块常常被用来为测试文件提供必要的激励。有两种不同的方法来实现并行的激励:一种是绝对时间激励,另一种是相对时间激励。

在绝对时间激励中,所有的仿真时间值都是相对仿真时间零点定义的。而在相对时间激励中,一般会提供初始化值,然后等待事件来触发激励向量。两种方法都可以根据设计者的需要在同一个测试文件中使用。

下面分别是两种方法产生激励的例子。

(1)绝对时间。

initialbegin

Reset=1;//仿真时间零点激励

Load=0;//仿真时间零点激励

Count_UpDn=0;//仿真时间零点激励

#100Reset=0;//绝对时间100激励

#20Load=1;//绝对时间120激励,相对上一个时间点20

#20Count_UpDn=1;//绝对时间140激励,相对上一个时间点20

end

(2)相对时间。

always@(posedgeclock)

TB_Count=TB_Count+1;//绝对时间的递增

initialbegin

if(TB_Count=5)begin//触发事件,产生下列激励

Reset=1;

Load=0;

Count_UpDn=0;

end

elsebegin//触发事件,产生下列激励

Reset=0;

Load=1;

Count_UpDn=1;

end

end

initialbegin

if(Count==1100)begin//触发事件,产生归零激励,并显示结果

Count_UpDn=0;

$display(TerminalCountReached,nowcountingdown.);

end

end

值得注意的是,VerilogHDL语言的initial模块之间是并行执行的,但是initial模块内部是顺序执行的。也就是说,测试文件的激励顺序在仿真时间零点同时启动并行模块,然后根据各个模块的内部激励顺序产生激励向量。

3.结果输出

测试文件通过关键词$display和$monitor来实现结果的输出。下面是使用VerilogHDL语言实现在终端上显示结果的例子:

//在终端中打

仿真验证 仿真测试文件 FPGA Testbench 相关文章:

- FPGA系统设计的仿真验证之: FPGA设计仿真验证的原理和方法(06-05)

- FPGA系统设计的仿真验证之: 功能仿真和时序仿真的区别和实现方法(06-05)

- 说说FPGA系统的仿真和测试(02-27)

- 在采用FPGA设计DSP系统中仿真的重要性 (06-21)

- 基于 DSP Builder的FIR滤波器的设计与实现(06-21)

- 基于FPGA的快速并行FFT及其在空间太阳望远镜图像锁定系统中的应用(06-21)