基于FPGA的视频传输流发送系统设计

时间:06-06

来源:互联网

点击:

3.3 8B/10B编码模块

8B/10B编码模块是ASI接口转换的核心之一。DVB-ASI数据编码层的传输规约包括串行编码规则、专用字符和差错控制。它采用DC平衡的8B/10B传输码。这种码把每一个8bit数据字节变换成符合直流平衡特性的10bit码字。这种码通过无效传输码点和“运行”的不均衡性来提供差错校验。作为超出对数据字节进行编码需要的额外码点,规定了专用字符。

系统以字节同步的方式接收MPEG-2传送包,接收的参考时钟是采用固定的27MHz的时钟频率。接着,对字节进行8B/10B编码,对出现的每一个8bit字节产生一个10bit的字,使这些10bit字通过以固定输出比特率270Mbps工作的并/串转换。

将8B/10B编码划分为3个模块实现,较好地反映了8B/10B编码的特点,实现流程清楚,容易编写代码。具体实现步骤为: ① 判断是特殊字符还是数据; ② 若是特殊字符(3B4B),根据RD极性直接取值; ③ 若是数据,根据RD极性和前一个10bit模块的编码情况确定当前6 bit的取值; ④ 根据当前6 bit编码值确定当前4 bit的编码取值。⑤ 将当前6 bit编码和当前4bit编码组成当前10bit编码输出。

3.4 并串转换模块

在完成8B10B编码以后,将信号送至并串转换模块转换为串行数据流,通过270MHz时钟将串行信号送出,ASI接口采用两线差分方式进行串行数据传输。

4 测试结果

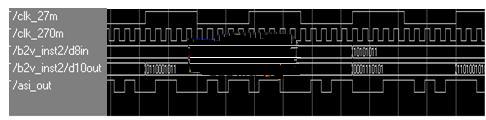

首先对ASI发送系统进行功能仿真,仿真平台为ModelSim6.0,本设计中,ASI发送系统的输入输出的仿真波形如下图所示:

仿真结果表明,输入信号与编码信号之间顺序相差一个码元周期,输出抖动被完全消除。

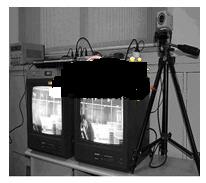

本文中的ASI接口测试由Honeywell公司的摄像头、自行研制的MPEG2编码板(视频压缩芯片为MB86391)、MPEG2解码器、显示器构成,如图3所示。

ASI发送测试为:Honeywell公司的摄像头和自行研制的MPEG2编码板输出符合MPEG2标准的TS流,通过标准SPI口送给本文的ASI转换系统的SPI输入,而经SPI到ASI的转换,通过BNC接头的有线电缆送给解码器的ASI口输入,解码后的视频输出送给显示器,连续播放数十小时,图像清晰且显示正常无误。

实验结果证明,采用本文方法设计的ASI发送系统,符合标准ASI接口规范,能有效可靠的实现SPI-ASI的编码功能和高速串行数据流的发送功能。

5 结语

本文作者创新点: 在分析ASI发送系统机理的基础之上,提出一种使用FPGA完成ASI发送系统的实现方案,并使用VHDL语言在Altara的FPGA上实现了硬件电路,仿真结果和实际测试完全正确。该方案层次分明、结构简洁、编码速度快、输出抖动小,与现有的使用专用芯片CY7B923的方法相比,具有更大的灵活性,为高速ASI数传的应用前端提供了条件。

8B/10B编码模块是ASI接口转换的核心之一。DVB-ASI数据编码层的传输规约包括串行编码规则、专用字符和差错控制。它采用DC平衡的8B/10B传输码。这种码把每一个8bit数据字节变换成符合直流平衡特性的10bit码字。这种码通过无效传输码点和“运行”的不均衡性来提供差错校验。作为超出对数据字节进行编码需要的额外码点,规定了专用字符。

系统以字节同步的方式接收MPEG-2传送包,接收的参考时钟是采用固定的27MHz的时钟频率。接着,对字节进行8B/10B编码,对出现的每一个8bit字节产生一个10bit的字,使这些10bit字通过以固定输出比特率270Mbps工作的并/串转换。

将8B/10B编码划分为3个模块实现,较好地反映了8B/10B编码的特点,实现流程清楚,容易编写代码。具体实现步骤为: ① 判断是特殊字符还是数据; ② 若是特殊字符(3B4B),根据RD极性直接取值; ③ 若是数据,根据RD极性和前一个10bit模块的编码情况确定当前6 bit的取值; ④ 根据当前6 bit编码值确定当前4 bit的编码取值。⑤ 将当前6 bit编码和当前4bit编码组成当前10bit编码输出。

3.4 并串转换模块

在完成8B10B编码以后,将信号送至并串转换模块转换为串行数据流,通过270MHz时钟将串行信号送出,ASI接口采用两线差分方式进行串行数据传输。

4 测试结果

首先对ASI发送系统进行功能仿真,仿真平台为ModelSim6.0,本设计中,ASI发送系统的输入输出的仿真波形如下图所示:

仿真结果表明,输入信号与编码信号之间顺序相差一个码元周期,输出抖动被完全消除。

本文中的ASI接口测试由Honeywell公司的摄像头、自行研制的MPEG2编码板(视频压缩芯片为MB86391)、MPEG2解码器、显示器构成,如图3所示。

ASI发送测试为:Honeywell公司的摄像头和自行研制的MPEG2编码板输出符合MPEG2标准的TS流,通过标准SPI口送给本文的ASI转换系统的SPI输入,而经SPI到ASI的转换,通过BNC接头的有线电缆送给解码器的ASI口输入,解码后的视频输出送给显示器,连续播放数十小时,图像清晰且显示正常无误。

实验结果证明,采用本文方法设计的ASI发送系统,符合标准ASI接口规范,能有效可靠的实现SPI-ASI的编码功能和高速串行数据流的发送功能。

5 结语

本文作者创新点: 在分析ASI发送系统机理的基础之上,提出一种使用FPGA完成ASI发送系统的实现方案,并使用VHDL语言在Altara的FPGA上实现了硬件电路,仿真结果和实际测试完全正确。该方案层次分明、结构简洁、编码速度快、输出抖动小,与现有的使用专用芯片CY7B923的方法相比,具有更大的灵活性,为高速ASI数传的应用前端提供了条件。

- 在采用FPGA设计DSP系统中仿真的重要性 (06-21)

- 基于 DSP Builder的FIR滤波器的设计与实现(06-21)

- 基于FPGA的快速并行FFT及其在空间太阳望远镜图像锁定系统中的应用(06-21)

- 3DES算法的FPGA高速实现(06-21)

- 用FPGA实现FFT算法(06-21)

- FPGA的DSP性能揭秘(06-16)