基于EDA技术的无线抢答系统的设计

时间:08-14

来源:互联网

点击:

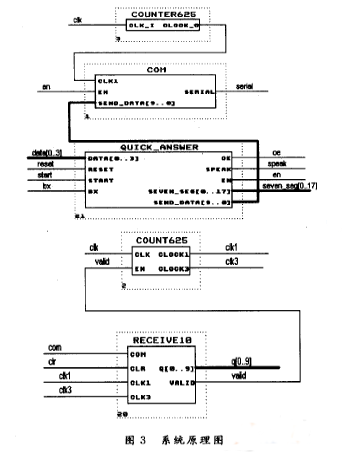

答终端编码接收模块、串行发送模块、串行接收模块。在Max-f-Plus II 10. 0中设计输人各个模块的VHDL的程序后,生成库器件并合成系统原理图如图3所示。以下简要介绍抢答终端编码接收模块和串行发送模块的程序设计。

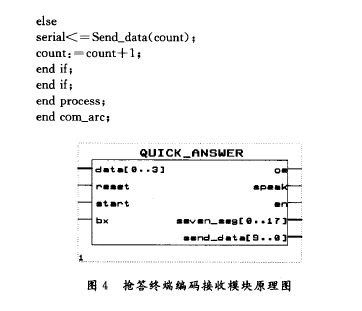

图4为生成的该模块原理图,其VHDL源程序如下:

3.1.2串行发送模块

如图4所示,该模块将抢答终端编码接收模块输出的抢答终端的编码按照串行异步通讯规则发送给人机接口电路。在串口通讯中,我们约定的帧格式为1位开始位+8位数据位+1位停止位,没有校验位,通讯波特率为9600。根据约定,该模块输出数据为10位,在发送完10位后,就停止发送,并使发送端电平处于逻辑1,然后等候下次的发送。其VHDL源程序如下:

3. 2上位机PC端的演示程序

本软件是在VB 6.0环境下开发的,并利用其数据管理功能,建立比赛题库并提供管理界面。其与主控制器之间的串行口通信设计部分充分利用了Mscomm串行口通信控件。由于该控件提供通过串口发送和接收数据的串行通信能力,包括了全部Windows API中关于串行通信的16个函数所完成的功能,而且开拓了更多使用户设计方便的对象属性来满足不同用户不同业务的需求,因此给编程带来极大的方便。

本软件在PC环境下运行,包括以下几个功能:根据设定自动抽出比赛题目、控制主控制器的工作、声光效果显示抢答终端编号并倒数计时、现场效果渲染等。详细程序在此不再赘述。

4结语

经过反复试验,该系统运行稳定,操作方便,达到了预期的设计效果,具有可操作性强、现场效果好的特点,已经在知识竟赛等相关活动中实际使用。

- 嵌入式系统设计方法的演化——从单片机到单片系统(01-28)

- Proteus在单片机教学和科技制作中的应用与实践(03-02)

- FPGA 原型设计:软件最重要!(03-21)

- 电子系统设计自动化方法和设计环境的研究(07-21)

- SoC:IP是新的抽象(10-24)

- 鳍式场效晶体管寄生提取的复杂性(12-26)