基于LabVIEW FPGA模块的FIFO深度设定实现

为了解决基于LabVIEWFPGA模块的DMAFIFO深度设定不当带来的数据不连续问题,结合LabVIEWFPGA的编程特点和DMA FIFO的工作原理,提出了一种设定FIFO深度的方法。对FIFO不同深度的实验表明,采用该方法设定的FIFO深度能够比较好地满足系统对数据连续传输的要求。研究结果对深入展开研究和工程设计具有一定的指导意义。

引言

数据进入FPGA的速率高于传出的速率,持续的传输会造成数据的溢出,断续的传输可能会造成数据不连续。使用基于LabVIEW FPGA的DMA FIFO作为主控计算机和FPGA之间的缓存,若DMAFIFO深度设置的合适,FIFO不会溢出和读空,那么就能实现数据输出FPGA是连续的。

本文在介绍了LabVIEW FPGA模块程序设计特点的基础上,结合DMA FIFO的工作原理,提出了一种设定FIFO深度的方法,解决了FIFO溢出、读空的问题,实现了数据的连续传输。实验结果表明该方法正确、可行,程序设计满足系统对数据传输连续性的要求。

1 LabVIEW FPGA模块

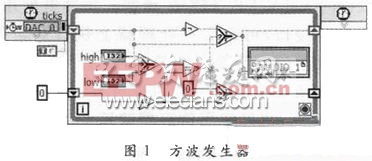

LabVIEW FPGA是LabVIEW的一个子模块,使用该模块可以通过图形化的编程对NI公司RIO(Reconfigurable I/O)设备上的FPGA进行配置。图形化的程序直接在硬件上实现,通过对RIO设备上的I/O接口的控制,可以灵活地对I/O信号进行分析和处理,表现出比固定I/O硬件更加优异的特性。使用LabVIEWFPGA模块开发出来的系统具有开发周期短、结构模块化、升级方便等优点。例如,图1表示了一个用LabVIEW FPGA模块设计的程序,在FPGA上实现方波发生器。该方波发生器通过数字接口DIO_1输出方波,其占空比和周期可调。LabVIEW FPGA模块在程序的设计与实现上都展现出了极大的灵活性。

1.1 LabVIEW FPGA程序开发流程

使用LabVIEW FPGA模块开发应用程序的流程如图2所示。首先创建FPGA vi,之后用FPGA设备仿真器在主控计算机上运行程序,反复地调试、修改,直至程序正确无误。然后编译FPGA vi,并把程序下载到FPGA上。FPGA部分的程序完成后,再根据需要在主控计算机上创建用户界面程序Host vi,最终就完成整个系统的设计。

FPGA设备仿真器的打开方法是:首先在“项目浏览器”窗口中的打开“我的电脑”子菜单,右击子菜单中的“FPGA Target”并在快捷菜单中选择“Execute vion”下一级子菜单中的“Development Computer with Simulated I/O”。然后再在FPGA vi中点击“Run”按钮,这时程序在FPGA的设备仿真器上运行。

1.2 开发FPGA vi

发应用程序的第一步是创建用于配置PXIe-5641R板载FPGA的程序。在FPGA vi中可以实现算法逻辑,包括信号同步,定制数字通信协议,板载控制和预警处理判决机制等功能。通过LabVIEW FPGA模块,可使用LabVIEW开发环境和许多类似的功能。但是由于FPGA不支持浮点操作,所以LabVIEW FPGA模块较之LabVIEW完整Windows版开发软件缺少了一些操作符和分析函数。另外,由于PXIe-5641R板卡没有硬盘和操作系统,因此不支持文件I/O和ActiveX功能。LabVIEW FPGA模块的函数面板如图3所示。

硬件对象不管是FPGA设备还是FPGA仿真器,都可以访问LabVIEW FPGA函数。仿真器使用RIO设备的I/O接口,可在主机处理器上执行逻辑算法。检验vi设计中的一些简单性错误,避免不必要的反复编译,尤其是在程序比较大的时候可节省大量的时间,提高编程效率。也可使用仿真器验证vi的执行流程,但无法验证硬件的确定性,若需要验证硬件性能的确定性,必须对FPGA vi进行编译。与其他FPGA开发工具一样,根据应用程序的复杂程度和计算机资源的不同,编译步骤可能要花上几分钟到几个小时的时间。

1.3 开发Host vi

在FPGA vi完成调试、编译、下载到板卡之后,就需要在主控计算机上创建一个用户界面程序Host vi。在用户界面应用程序中可以完成一些实时性要求不高的操作,例如配置系统参数,管理数据等。Host vi通过FPGA接口函数与FPGA vi进行通信,以及处理中断。FPGA接口函数面板会在安装LabVIEW FPGA模块之后,自动添加到LabVIEW的函数面板中。LabVIEW函数面板中的FPGA接口函数面板如图4所示。

2 不同时钟域的数据连续传输

本文中的中频信号生成系统是将主控计算机模拟生成的数据通过FPGA送到AD9857发送出去。数据进入FPGA的速率为52 MB/s,由于计算机的非实时性呈现断续的形式,其实际的速率要低一些;数据传出FPGA时,其数据位宽为16 b,输出频率为10 MHz,固其持续传输速率为20 MB/s。数据进入FPGA的速率高于出FPGA的速率,这就造成数据在不同时钟域之间传输的问题。为了避免数据的溢出和保证数据连续性,本文使

- 基于LabVIEW RT的自定义流程测控系统(10-30)

- 基于LabVIEW的语音分析平台的实现(10-30)

- 基于示波器卡和LabVIEW的马达编码器测试系统(11-06)

- 基于虚拟仪器的网络虚拟实验室构建(11-06)

- 运用LabView控制DS3900串口通信模块(02-02)

- 采用模块化仪器,对新兴音频和视频应用进行测试(02-19)