基于TMS320F28033的20MHz手持式双踪袖珍示波器

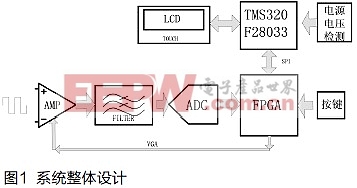

摘要:项目实现的是一个手持式双踪袖珍示波器,以TMS320F28033为核心,由信号放大电路、信号采集电路、数据存储与处理模块、系统控制与显示模块等部分组成。信号放大电路先对输入信号进行程控增益放大。信号采集电路使用高速ADC对信号进行模数转换,数据送入以FPGA为核心的数据存储与处理模块。TMS320F28033控制液晶显示和触摸输入。系统具有体积小、输入阻抗小、功耗小等特点。

引言

基于性能够用、体积够小的原则,本项目设计的示波器解决了以下几个问题:

(1)利用新颖的设计取代了传统示波器中必需的继电器,而同样实现DC/AC耦合的电切换,体积很小;

(2)实现了很高的输入阻抗和很小的输入电容;

(3)主控采用了功能强大,外设丰富,功耗低的TMS320F28033,简化了系统设计,减小了体积,有助于设计最终实现了真正的袖珍与便携。

系统方案

系统整体设计见图1。主控TMS320F28033负责控制液晶和触摸输入,即“人机界面”。使用GPIO模拟8080总线控制液晶,使用具有输入输出功能的AIO以及内部ADC实现触摸输入。通过SPI与FPGA交换数据,并对数据进行处理和显示。系统的数字校准也是在其中完成的。同时还有检测电源电压的功能。FPGA把高速ADC输出的数据流存储在内部SRAM中,通过PWM控制输出占空比,滤波后以其直流电平控制压控增益放大器的增益,通过IO控制模拟开关的通断实现DC/AC耦合的切换。FPGA内部逻辑实现了信号的触发控制,通过SPI把数据传送到TMS320F28033。

信号进入系统,先后经过跟随保持、直流/交流耦合、程控增益放大、带宽限制滤波器,再进入高速ADC——ADS62P22。为了防止频谱混叠,对输入高速ADC的信号使用阻容网络进行了带宽限制。低通阻容网络的输入带宽是20MHz。

FPGA 示波器 TMS320F28033 201209 相关文章:

- 远程测控中嵌入式Web服务器的FPGA实现(10-30)

- 基于DSP Builder的DDS设计及其FPGA实现(11-03)

- 基于FPGA的DDS调频信号的研究与实现 (11-04)

- 使用混合信号示波器验证测量混合信号电路(11-05)

- 基于速度匹配软件的网络芯片仿真方法(11-06)

- 利用FPGA实现原型板原理图的验证(11-07)