基于FPGA的监测数字示波器设计

广泛分布在FPGA的各个区域,离逻辑单元电路较近,用于存储各逻辑电路处理的信号。数字示波器存储的波形数据量较大,所以在双口RAM采用Block RAM实现。

?

?

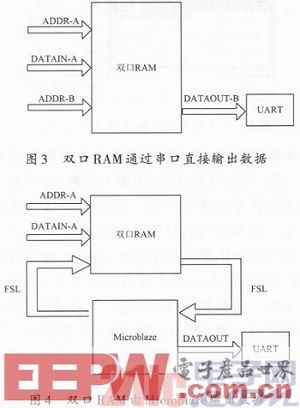

AD9244输出的数字信号为14位,所以RAM的数据宽度设置为16位,双口RAM数据读、写可采用相同的时钟控制;波形存储深度设定为1 024,即双口RAM存储1 024个采样点数据,所以双口RAM存储器共占用16 Kb RAM空间。由于核仪器工作在高辐射污染区,人员一般不能进入,通信一般采用无线通信方式,所以数据常采用串口通信方式。双口RAM数据直接经串口输出的原理图如图3所示。双口RAM数据经FSL总线由Microblaze处理器输出原理图如图4所示。A口用于RAM信号存储,数据宽度16位,深度1 024。B口用于RAM数据输出,若用ISE编写串口程序,B口数据宽度为8位,深度2 048;若采用PLB或FSL总线IP核方式,B口数据宽度定制为16位(16位RAM数据加载到32位总线的低16位上,总线高16位补零),深度为1 024。

2.4 数字波形数据存储及波形输出

FPGA双口RAM(Dual RAM)数据输出控制可采用多种模式:存满输出模式、定时输出模式和波形参数触发模式,可用串口指令控制各模式间切换。存储满模式工作原理为Dual RAM存储1 024点数据和串口输出数据交替工作,每存储满一次数据就通过串口输出数据,串口输出完数据后重新采集和存储数据;定时输出为Dual RAM存储1 024采样点数据,存储满后待定时信号,设定每几秒输出一次波形数据;脉冲波形参数触发模式类似于通用数字存储示波器的输出触发模式,在波形数据写入RAM前对波形参数(如脉冲幅值、脉冲形状、脉冲宽度等)数据进行提取,当波形参数在需要的范围时,FPGA输出数字波形,该模式可以采集并输出指定参数的脉冲信号,可以对核爆炸的光辐射、电磁脉冲、冲击波、放射线沾染等各种效应信号波形进行录制、回放和精确分析,从而实现核爆的自动监测和识别。

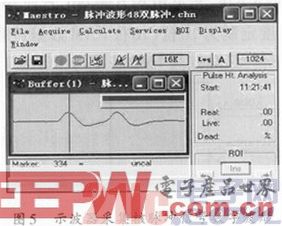

3 对核脉冲信号进行测试分析

利用示波器可对核爆炸γ射线、光辐射、冲击波等传感器信号进行波形存储,通过存储信号特征参数判断核爆炸方式。示波器采集的NaI(T1)探测器经成形后的近高斯核脉冲信号如图5所示。将脉冲数字波形用OREC谱分析软件进行分析,由于输出的值是数字多道工作的实际值,比用通用示波器更准确,可进行更准确的分析。

?

?

脉冲波形形状:图5所示波形和通用数字示波器输出波形一致,为近高斯波形,图像更清晰,是判断成形电路信号成形质量的重要依据。该波形测量方法是在强辐射环境下观察和分析脉冲堆积的很有效方法及堆积判弃处理的重要依据。从图5还可看出,脉冲波形下冲偏大,需对探头放大成形电路进行调节,减小高斯成形电路的下冲。可根据脉冲的形状(混叠情况)初步判断放射源的强弱。图5所示,波形为示波器连续采得两个核脉冲信号。波形图中若测得脉冲波形密集,或出现脉冲重叠,则说明源较强;若脉冲稀疏,则源较弱。

基线值测量:该数值是探头放大成形电路调节和数字多道基线扣除的重要依据。图5中可读出基线均值为1 072,基线值的范围是1 069~1 074,波动大小为5,本次测量波形基线值偏大,需要对探头进行调节或在数字多道中对基线值进行扣除。

脉冲宽度测量:该值是抗干扰设计和基于脉宽测量反堆积的重要依据。可读出正脉冲(高于基线均值的取样点)共约125左右个取样点,脉宽为2.5μs,可以计算出核脉冲成形的宽度。如果脉冲宽度过小,则可能是干扰信号;过大可能是脉冲堆积信号。

脉冲幅值测量:该值是数字多道脉冲幅度分析器设计最重要的数据。可读出两个脉冲数字波形的最大值分别为1 384和1 381,扣除基线值后幅值为312和309;最大值左、右两个采样点的值与峰值差值也小于基线波动值,说明在该采样频率下,用逐点比较冒泡法提取幅度值是可靠的。脉冲幅度大小可基本看出射线的能量,从测量看出,幅值为312,对应为312道,通过数字多道能谱分析,其能量约660 keV,和波形测试用的放射源一致。所以从波形的幅度规律,可大致看出放射源主要是什么核素。

脉冲幅值时间测量:可读出在脉冲到来后的第66个采样点获取最大值。

噪声测量及抗噪处理:从图5波形还可看出,信号中存在一定的噪声,所以在数字多道处理时,可用DSPIP核对脉冲波形进行数字平滑处理,同时可通过设定一定的噪声容限,幅值低于噪声容限的都看作噪声,高于噪声容限的信号才可能是有效信号,对数字多道进行抗干扰处理。

脉冲波形和幅度谱比较分析:由图5信号源高斯波形代替核脉冲信号,可用该示波器的波形图和幅度谱图对比,比较脉冲幅度和幅度谱数据,可以对数字多道能谱

- 远程测控中嵌入式Web服务器的FPGA实现(10-30)

- 基于DSP Builder的DDS设计及其FPGA实现(11-03)

- 基于FPGA的DDS调频信号的研究与实现 (11-04)

- 使用混合信号示波器验证测量混合信号电路(11-05)

- 基于速度匹配软件的网络芯片仿真方法(11-06)

- 利用FPGA实现原型板原理图的验证(11-07)