基于MSP430与FPGA的多功能数字频率仪设计*

作者/ 任欢 颜逾越 厦门大学嘉庚学院 信息科学与技术学院(福建 漳州 363105)

摘要:本文采用以FPGA为主,MSP430为辅的框架系统处理方式设计了多功能数字频率仪。该装置采用低频直接测周期,高频等精度多周期同步测量的方法,通过进一步优化标准时钟频率的设置,克服了传统测频方法在高精度要求方面的缺陷。将MSP430作为控制处理核心、FPGA作为信号处理单元,将高效控制与快速运算能力相结合,实现正弦波频率、两路方波信号时间间隔以及矩形脉冲占空比的测量。测试表明,该装置具有高精度、高稳定性、装配简易和操作便利的特点。

引言

随着电子产业的蓬勃发展,新兴产业对频率等参量测量结果的快速性、稳定性、精确性等性能指标提出了更高的要求[1]。目前,信号频率的测量已有多种测量方案,如过零检测法[2]、离散傅里叶变换[3]、离散卡尔曼滤波[4-5]等。其中存在对高频信号的快速测量的局限性、频谱泄漏[6]以及准确性有待提高[7]等问题。本文采用高速现场可编程逻辑阵列(FPGA)及超低功耗单片机(MCU),结合多周期测量原理,通过进一步优化标准时钟信号频率的设置,使用低频时钟计数法直接测周期,高频等精度多周期同步测量法测频率的方法,实现对待测信号频率、占空比、两路信号时间间隔等参量的高精度测量。

1 系统设计思路

1.1 系统总体结构

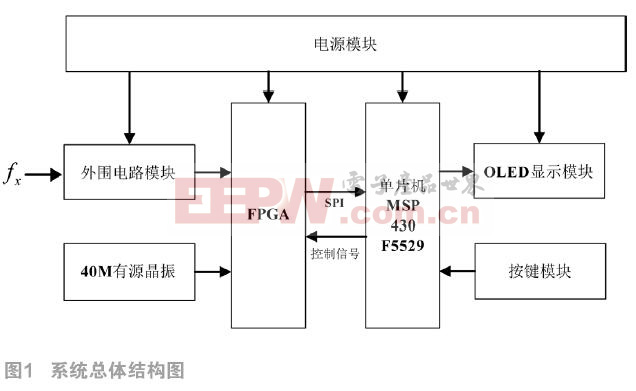

系统由Altera公司CycloneII EP2C8Q208C8型号FPGA、TI公司MSP430F5529型号MCU、外围电路模块、显示模块、按键模块和电源模块构成,系统的总体结构如图1所示。其中,MCU是本系统的控制中心,主要负责数据接收、逻辑处理和命令传达;FPGA是本系统的核心测量模块,主要负责利用由其内含的计数模块而构成的等精度频率测量模块、高电平时间计数模块、低电平时间计数模块、时间间隔测量模块进行高频信号的频率、低频信号的周期、单路方波信号的占空比和两路方波信号时间间隔的测量,并根据MCU给定的控制信号,通过SPI协议发送相应的测量数据至MCU中;外围电路模块是本系统的输入信号调理模块,主要负责将待测信号f(x)通过一系列的放大、整形等处理输出为FPGA可直接判别并计数的方波信号;显示模块主要用于已测得信号的频率、占空比、时间间隔等参量的显示,并由按键模块进行数据刷新。

1.2 时间及频率测频原理

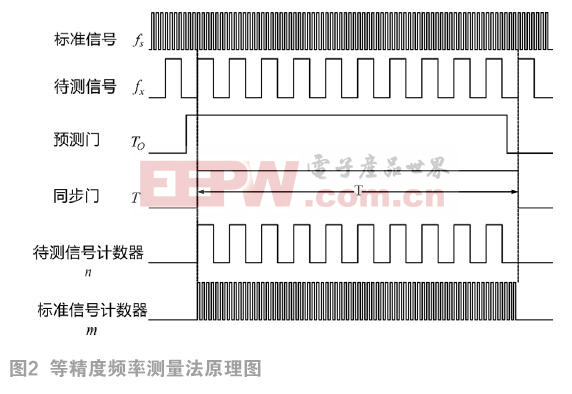

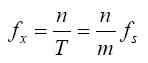

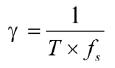

等精度频率测量法是指在给定一种标准时钟信号的情况下,通过对待测信号的上升沿进行多次识别及计数,从而得到待测信号频率的方法。等精度频率测量法的原理图如图2所示,若待测信号在标准时钟信号上升沿个数为m的T秒时间内,上升沿个数为n个[8],则待测信号频率为:

(1)

(1)

其中,fx为待测信号频率,fs为标准时钟信号频率。

将式(1)进行微分及相应变换可得:

其中,dfs/fs为标准信号误差,即晶振误差,由于晶振稳定性高,这一部分误差可忽略不计。

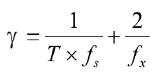

则频率测量误差为:

(4)

(4)

由此可见,理论中测量误差与待测信号频率参数无关[9-10],增长标准时钟信号的同步时间T或增大时钟信号的频率皆可进一步提高测量精度,且等精度测频法无法对频率低于1/T低频信号进行测量。另一方面,在实际测试中,FPGA计数结果可能因硬件延迟存在着两个计数值的固定误差,则有实际误差为:

(5)

(5)

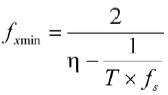

若要求测量误差小于η时,则符合精度的待测频率fx的最小值为:

(6)

(6)

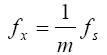

直接测周法是一种对待测信号一个周期内标准时钟信号进行计数,从而测量待测信号频率的方法,其测量原理图如图3所示。若标准时钟信号在待测信号一个周期内上升沿个数为m个[11],则待测信号频率为:

(7)

(7)

同理可得:

(8)

(8)

同理,省略掉晶振误差,且考虑FPGA硬件延迟后,可得直接测周法的测量误差为:

(9)

(9)

由此可见,理论中测量误差与待测信号频率参数有关,若要求测量误差小于时,则符合精度的待测频率fx最大值为:

(10)

(10)

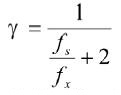

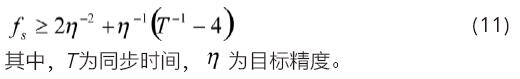

若要对低频段采用直接测周法,高频段采用等精度测频法实现对整个通带的信号频率测量,则必须有![]() ,即必须将标准时钟信号频率设置为:

,即必须将标准时钟信号频率设置为:

本文来源于中国科技核心期刊《电子产品世界》2016年第9期第65页,欢迎您写论文时引用,并注明出处。

1.3 外围电路设计

外围电路模块的主要作用是通过一系列的放大、整形等处理实现对输入信号的调理,使输出为FPGA可直接判别并计数的TTL信号。首先,FPGA作为一种现场可编程门阵列,只能对数字信号进行操作,因此,调理电路的输出信号幅度不得低于2.4V;其次,由于FPGA为本系统的信号测量单元,且通过捕捉待测信号上升沿来实现对待测信号频率的测量,因此,调理电路输出信号的上升沿必须保证在单个时钟脉冲之内,即要求输出信号的上升时间较短。

本系统的外围电路包括高频处理、中

多周期同步测量 标准时钟频率 占空比 FPGA MSP430 201611 相关文章:

- 函数信号发生器的认识(03-08)

- 方波信号发生器的设计(08-10)

- 远程测控中嵌入式Web服务器的FPGA实现(10-30)

- 基于DSP Builder的DDS设计及其FPGA实现(11-03)

- 基于FPGA的DDS调频信号的研究与实现 (11-04)

- 使用混合信号示波器验证测量混合信号电路(11-05)