基于SOPC的人脸检测系统的设计

人脸检测技术是计算机视觉领域非常重要的研究内容,正受到越来越多的关注。但传统的PC机平台上人脸检测系统体积庞大、不易携带、费用高等缺陷。采用通用DSP和多核处理器实现的话,价格昂贵、系统的可拓展性差。本文采用了xilinx公司的Zynq-7000系列芯片作为人脸检测系统实现平台。Zynq-7000系列是Xilinx公司推出的行业第一个可扩展处理All Programmable解决方案平台,旨在为视频监视、汽车驾驶员辅助以及工厂自动化等高端嵌入式应用提供所需的处理与计算性能水平。本设计采用的是Zynq-7000的XC7Z 02SOPC芯片,该芯片集成了Crotex—A9 MPCore双核处理器系统,同时内部集成了丰富的可编程逻辑资源,该部分包含约1.3M个等效逻辑门数和220个DSP Slices。这些资源提供了灵活可拓展的图像处理解决方案。

人脸检测算法有很多,主要可以分为:基于知识的方法、基于特征的方法、基于模板的方法和基于统计的方法。其中以Adaboost为统计的人脸检测算法是无论在检测精度还是检测速度上,在计算机视觉领域被认为已经达到很高的水准。

1 Adaboost人脸检测算法原理

Adaboost人脸检测算法是基于统计模型的方法,该方法给出了一个实时的、稳定的检测架构。此方法会从许多典型的数据信息中获取并进行特定的分析,得出人脸图像,这也是人们普遍使用它进行人脸识别的最根本原因。这一算法主要有3个方面的特点:利用积分图(Integral Image)快速计算Haar特征;利用Adaboost学习算法将Haar特征生成的弱分类器(Weak Classifier)组合成一个强分类器((Strong Classifier);将强分类器串联形成级联分类器(Cascade Classifier)。

1.1 Haar特征及积分图的计算

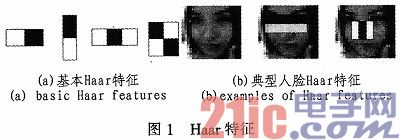

Haar特征又称矩形特征,指的是一系列矩形构成的结构,这种特征结构简单,利于快速计算。图1(a)是四种基本结构的矩形特征。把矩形特征中自色区域像素灰度值减去黑色区域的像素灰度值就得到该矩形特征的特征值。图1(b)矩形特征在人脸检测中的应用,这些典型的矩形特征能够很好把人脸和非人脸区分开来。

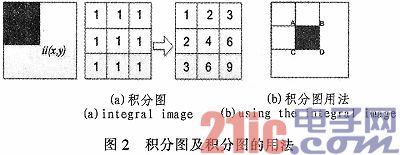

积分图能够快速算出Haar特征的特征值。如图2(a)所示,积分图像的定义;积分图图像的任意一点i(x,y)处的积分图像值ii(x,y)是原图像上该点的左上方所有像素的灰度值之和,即

引入积分图,计算任意矩形特征的区域的灰度值只需要4个参考点即可,图2(b)中灰色部分的矩形特征区域的灰度值可以通过A,B,C,D四个点的积分图来计算,即

sum=ii(AA)+ii(D)-ii(R)-ii(C) (2)

其中sum表示该灰色区域的灰度值。

1.2 Adaboost人脸检测算法

整个Adaboost人脸检测算法如图3所示,首先对图像进行预处理并计算检测图像的积分图,然后扫描其中每个N*N窗口,对于每个N*N窗口需要进入一个层次型检测结构(图示是一个三层结构每一层都是经过Adaboost算法训练得到一个强分类器),计算分类器中的各个Haar特征的特征值,再和阈值α相比较,进而选择得到一个该分类器的影响因子。对于每个分类器的检测中,所有的影响因子累加起来就是该窗口和人脸的相似度,最终把相似度与阈值β比较。若相似度的值小于β,则判定该窗口图像不是人脸图像,将排除该窗口并选择进入下一窗口,若相似度的值大于β,则判定该窗口图像是人脸窗口图像,该窗口可以到下个分类器进行检测。如果该窗口通过所有分类器,则该窗口就是人脸窗口,输出它的位置信息。将图像中所有N*N的窗口都检测完,第一轮的检测也就结束了。

一副图像种人脸的大小是不确定的,为了适应不同大小人脸的图像,在完成第一轮原始图像的检测后,需要放大检测窗口,并重复上述的步骤直到窗口不能放大为止。最后算法需要将所有检测窗口进行合并,将位置和大小相近的窗口合并在一起。

2 人脸检测系统SOPC实现

2.1 硬件设计方案

SOPC(System On Programmable Chip)就是要在单块芯片上搭建出整个系统,其设计的内容不仅包括硬件设计,还包括软件设计。基于SOPC的实现使得处理器、内存控制器等嵌入式系统所包含的硬件组成部分,都嵌入在芯片上。

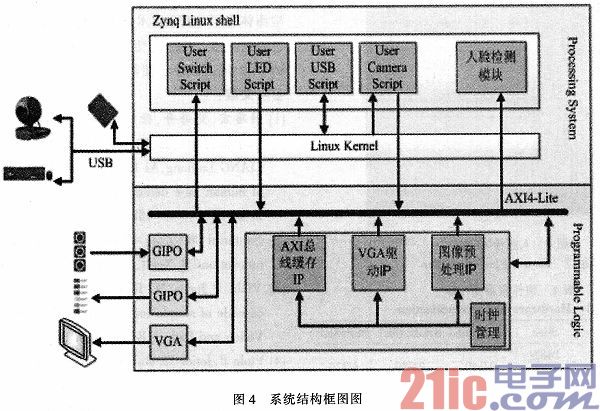

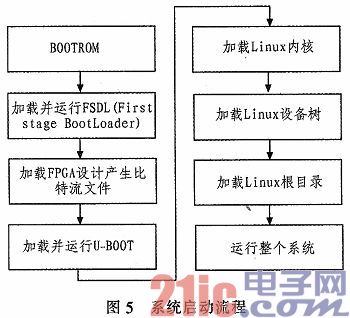

本系统依赖的硬件平台是Zedboard开发板,系统结构框图如图4所示,Zedboard的核心处理芯片是Xilinx公司的Zynq-7000芯片系列的XC7Z02,Zynq-7000芯片内部主要分为处理器系统PS(Processing System)和可编程逻辑PL(Programmable Logic)。PS部分内部嵌入了ARM Cortex—A9硬核模块,PL部分为FPGA,用户可自由设计自己的硬件逻辑。PS和PL之间的通信通过AXI4高级通信接口,图5显示利用Zynq进行SOPC开发的系统启动流程。

2.2 系统实现

图4给出了系统结构框图,其中PS部

- 基于肤色检测和人眼定位的人脸检测方法(09-11)

- 基于新的肤色模型的人脸检测方法(12-11)

- 基于SoPC的FIR滤波器设计与实现(07-18)

- 基于FPGA的语音录制与回放系统(09-18)

- 基于SOPC的智能电子血压计设计(06-19)

- 基于SoPC的FPGA在线测试方法 (10-09)