测试平台上的阻抗测试方案

t/s的差分和单端传输线的阻抗测量。这种 仪器具有65ps的阶跃信号发生器,因此支持对测试板和实际电路的高分辨率测量。另外,DTDR-65具有特别好的抖动性能 (Jrms<500fs),而这种性能通常是高端设备才有的。

同时开发的软件解决方案能够让非射频专家也能顺利完成阻抗的测量。这种解决方案不仅包含基本功能(比如设备控制),还包含用于显示线路阻抗的直观可操作功能。容差模板使得做出通过/失败(PASS/FAIL)声明非常简单。下面介绍了一些简单的应用例子。

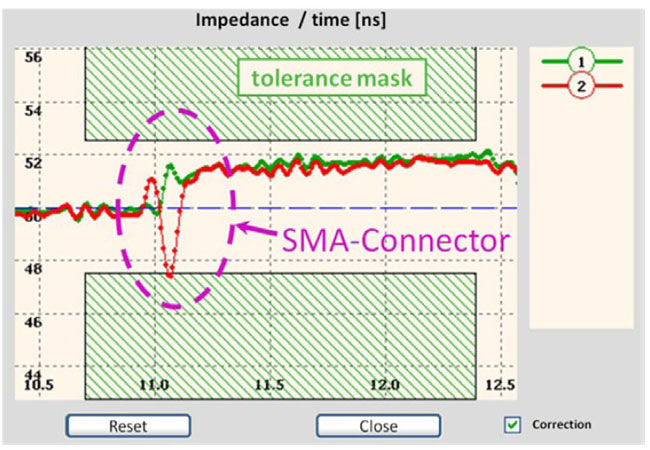

图3呈现的是RG 405同轴电缆的反射图,其中的同轴电缆分别按照组装规范(1)和没有按照组装规范(2)装配了SMA连接器。两种RG 405电缆的线路阻抗Z0≈51.5Ω,连接器区域的过渡非常明显。在错误安装连接器的情况下,电容下降(朝低阻抗变形)是可见的。当外部和内部导体安装 靠得太近时这种效应会频繁发生(也就是构建了一个电容)。

图3:正确安装SMA连接器(1,绿)和错误安装SMA连接器(2,红)时RG 405同轴电缆的反射图。

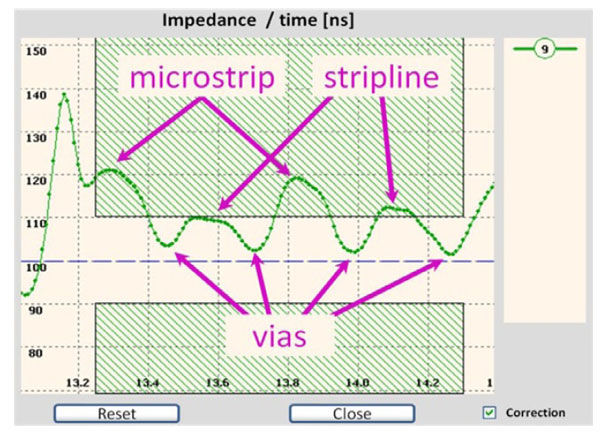

图4显示了4层印刷测试电路上的差分传输线的阻抗曲线。传输路径一开始是第一层(顶层)中的微带线,然后通过一个过孔转到第二层,此时仍然是微带线,再通过 第二个过孔回到第一层表面。这个路线经过几次反复,最终在第一层终止。显然这个测试电路不能达到100Ω的目标阻抗:微带线和带状线的特征阻抗分别是 Z0≈120Ω和Z0≈110Ω。从这张图中可以明显看出,过孔的电容因素会严重影响实际系统中的信号完整性,尤其是在高数据速率时更甚。

图4:在FR4基板的两个不同层上布线的差分线反射图。

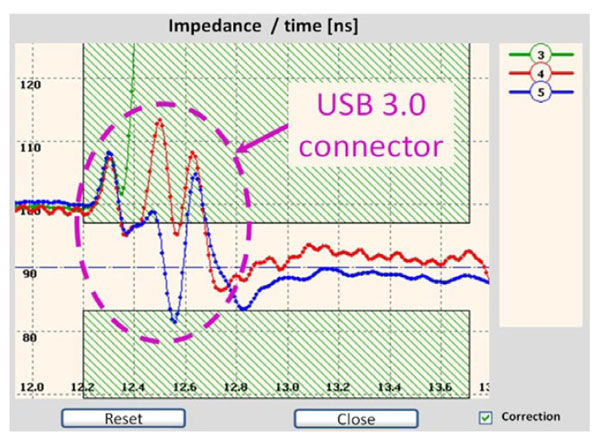

作 为最后一个例子,图5显示了USB 3.0连接器和电缆的反射图。USB 3.0组件的额定阻抗是Z0=90Ω±7Ω。TDR设备仍然工作在100Ω的参考阻抗上(时间范围t<12.2ns)。从测试适配器到USB 3.0连接器的转换引起的第一次反射发生在大约12.3ns,正如预期的那样与所有测量一致。曲线3(绿色)代表开放式适配器的结果,其中的快速阻抗上升 指示适配器的(高阻抗)末端。曲线4和5(红色和蓝色)代表两种不同的USB 3.0电缆组件,每个组件由一个适配器和一个后续电缆组成。虽然电缆都在规范之内,但适配器不符合规范。特别是红色曲线表明最大阻抗约为122Ω,产生了 严重反射,进而可能导致USB 3.0控制器降低数据速率。

总之,所有例子清楚地表明,开发人员能够利用DTDR-65直观 深入地观察传输路径。开发人员和质检人员的任务通常包含对所获得的结果进行容易理解的归档。这项任务非常重要,但遗憾的是非常耗时,而且单调乏味。不过这 种不受欢迎的工作现在可以用内置的自动化报告生成工具极大地简化,只需几次点击就能形成图形化和统计性的扩展性评估结果。另外,对大多数普通线路类型来说 还可以使用在线阻抗计算器。

图5:带开放电路(3)和两个不同USB 3.0电缆组件(4和5)的USB 3.0适配器的反射图。

支持广泛应用

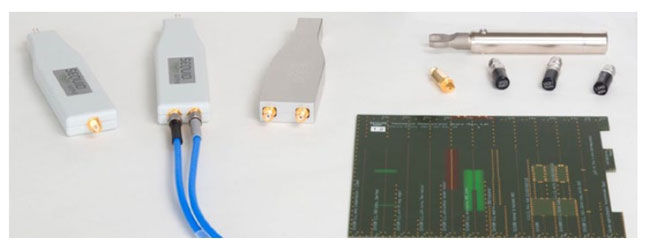

必要的附件包含了高质量的相位调整过的同轴电缆以及TDR探针,可用于不同类型应用:工业探针用于生产过程中的系列测量,高精度探针用于研发——见图6。DTDR-65还具有卓越的电磁屏蔽性能,完全可以在电池供电的移动应用中使用。

图6:用于时域反射计DTDR-65的不同探针和附件。

- S参数含义(12-03)

- 史密斯原图用在传输线的阻抗匹配很简单(06-28)

- 长传输线中信号振铃是怎么产生的呢?(07-18)

- 阻抗匹配决定了传输线技术的好坏(07-12)

- 高频PCB中传输线和特性阻抗(07-20)

- 信号传输线及其特征阻抗解析(10-18)