一款效率高达80%且功率损耗不足1W的3A、1.2VOUT 线性稳压器

引言

由于稳压器对压降的要求、效率的低下、因稳定性需要而对输出电容器过于严格的要求以及启动时太大的浪涌电流等原因,在大电流 (>1A) 低压降电压应用中采用线性稳压器一直都是个难题。TI 推出的具有双输入轨的 TPS74x01解决了上述问题。

线性稳压器拓扑概述

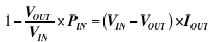

大电流应用中线性稳压器的主要缺点是效率较低,其效率可以通过 VOUT/VIN 计算得出。线性稳压器的功率损耗 (PLOST) 主要来自其封装,该功率损耗可以通过如下公式计算得出:

TO-263 或 D2PAK 封装是可用于线性稳压器的最大表面贴装封装。不计气流的话,该封装的最大功耗大约为 2.75W(假设该封装与一块较大的铜板焊接在一起用于散热)。带有 PMOS 旁路元件的大多数大电流低压降线性稳压器的最小输入电压范围为 2.5V~2.7V,其不但可以为内部 LDO 驱动电路供电,而且还足以驱动 PMOS FET 来提供较高的输出电流。

由于额外气流和/或需要对稳压器所产生的热量进行外部散热,因此,在输出电压低于 1.8V 和输出电流大于 2.5A 时使用带有 PMOS 旁路元件的线性稳压器就会显得不便,并且成本也会增加。

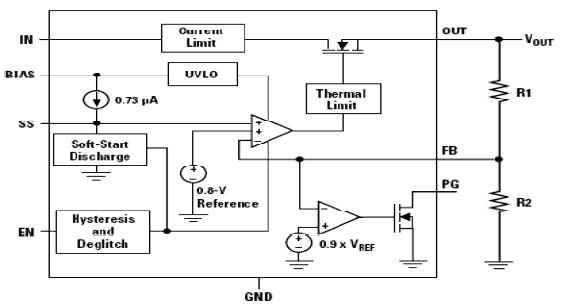

因为 NMOS FET 与具有相同电流速率的 PMOS FET 相比,一个较低的 rDS(on) 是其固有的特性,所以 NMOS FET 旁路元件只需要更低的 VIN-VOUT 压降即可提供相同强度的电流。但是,基于 NMOS 的稳压器的源极跟随电路结构要求 FET 门极至少为一个高于输出电压的阈值压降(一般为 1V)。稳压器需要一个内部充电泵来提供一个更高的栅极驱动电压,或是一个由电路中现有的 5V 或 3.3V 偏置电源产生的二次低功耗输入轨。这也就是设计基于 NMOS 旁路元件的双输入轨 TPS74x01 系列线性稳压器的原因。

压降

如图 1 所示,TPS74x01线性稳压器有两个输入电压,其中一个用来提供弱电流偏置电压以驱动控制 NMOS 旁路元件的内部电路,另一个用来进行二次功率输入。所有的内部电路均使用较高的偏置电压运行,旁路元件可以通过一个低压输入源实现稳压。实际上,输入功率 IN 只受制于输出电压和器件压降。

TPS74x01 有两种不同规格的压降。第一种规格为 VIN 压降,其专门针对那些希望通过采用一个外部偏置电压来实现较低压降的用户。该规格的稳压器偏置电压大于输出电压,至少为 1.62V。此类应用中,FPGA 收发器一般使用低纹波、1.2V 和 3A 的电源轨,该收发器内部 1.5V 和3.3V的开关电源分别提供输入电压和偏置电压。在该结构中,55℃时功耗为1.9W的 3×3mm QFN 封装功耗仅为 (1.5V-1.2V)×3A=0.9W,从而达到 1.2V/1.5V=80% 的效率。

第二种规格为VBIAS压降,该规格的压降专门针对那些希望将IN和BIAS引脚绑定在一起的用户。这样就可以在没有辅助偏置电压或不需要较低压降的应用中使用该器件。因为VBIAS要为旁路FET提供栅极驱动,所以VBIAS必须比VOUT高1.4V,同时压降受限于应用中所使用的BIAS。例如,TPS74201 可以提供一个由具有 3.3V/5V=66%效率的5V电源轨产生的3.3V、1.0A软启动电源(稍后讨论),并且功耗为(5V-3.3V)×1.0A=1.7W。

稳定性和瞬态响应

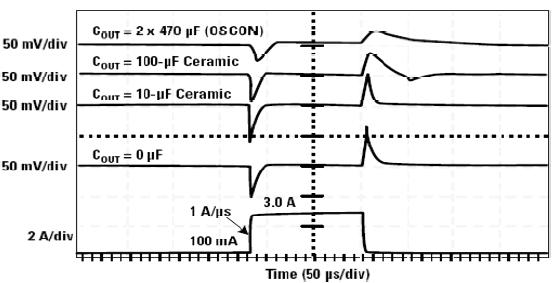

由于输出电容会产生一个控制环路极点和在负载情况下的阻抗以及基于输出电流的频率位置的变化,到目前为止,线性稳压器环路稳定性对模拟 IC 设计人员而言还是一个难题。与相同级别的共源结构的 PMOS 稳压器相比,带有 NMOS 旁路元件的源极跟随器结构稳压器的输出阻抗要更低,因此该稳压器比较容易进行功率补偿。这意味着,NMOS 稳压器的动极点 (moving pole) 频率要高于同等级别的 PMOS 稳压器,也要远远高于内部误差放大器的极点频率。为确保稳定性,比较传统的方法是在低频下逐步减少控制环路的响应,从而减少瞬态响应,或者用一个零极点与动极点相抵消,该零极点由一定数量的等效串联电阻 (ESR) 组成的输出电容产生。通过使用具有专利的反馈控制拓扑,配置为VBIAS=3.3V,VIN =1.8V和VOUT=1.5V的 TPS74x01 系列产品,可以实现无输出电容的情况下较快的瞬态响应(见图 2),同时在设置有 ESR 这种较大电容的情况下仍然保持稳定。负载瞬态响应之后并没有输出电压振铃,这表明稳压器在没有输出电容的情况下非常稳定。

由于 TPS74x01 系列产品在没有输出电容的情况下比较稳定,同时瞬态响应比较快,因此有足够的用于欠功率器件的局部旁路电容来满足大多数 FPGA 和 DSP 的瞬态响应需求。由于不再需要用于电源轨的多联大型电容器,从而降低了解决方案的总成本。

软启动和排序

大多数传统的线性稳压器启动较快,这是因为反馈环路可以感应低输出电压,并开启旁路 FET。在一

- 基于Multisim的直流稳压电源设计(06-21)

- 直下式LED背光源的设计与实现(02-13)

- 品能PN913移动电源技术方案深度剖析(04-11)

- 多功能太阳能移动电源箱的设计方案(12-16)

- RC延时电路简要分析(11-27)

- 首次使用Multisim软件进行电路仿真设计(12-09)