基于CPLD+MCU的新型光栅数显系统设计

Design of digital display system on raster based on MCU CPLD

摘要: 利用CPLD替代传统专用的ASIC来采样处理正交脉冲。利用高精度电压检测器配合增强型MCU实现掉电数据存储,从而实现新型光栅数显示系统的设计。

关键词: 光栅; 正交脉冲; 掉电数据存储; CPLD; EPM240; STC89C516RD

Abstract: The implement of sample and processing of quadrature pulse with CPLD are described in detail.The power failure data-store is realized with a high precision voltage monitor and MCU.So that a new display system on raster is design.

Keywords: raster; quadrature pulse; power failure data-store; CPLD; EPM240; STC89C516RD

1 引言

光栅数显系统主要用于普通机床,可直接显示机床加工的长度值,有助于提高加工精度和效率。目前国内市场上的光栅数显系统大多采用国外集成电路实现,研发成本高,且不便于操作人员使用。针对这种状况,研发了基于MCU+CPLD的新型光栅数显系统。该系统具有计数精度高、成本低、操作方便以及升级快等特点,能够处理高达5 MHz/s的正交脉冲,并在掉电时有效存储当前长度值,其数码管可显示关键的长度值,点阵式液晶屏还可显示相关的提示信息。

2 系统工作原理

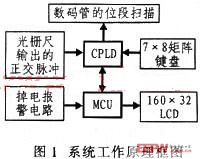

利用CPLD实现正交脉冲处理逻辑电路,而可逆计数器则用于处理计数光栅尺输出的正交脉冲,CPLD的高速并行处理能力可保证光栅尺输出信号无遗漏采样,从而确保计数的可靠性。可逆计数器的值通过MCU一系列运算后转换为机床加工的长度值,MCU再将其长度值回送至CPLD并在数码管上显示。

此外,CPLD还具有7×8键盘按键检测和去抖功能,将处理后的可靠按键送至MCU。MCU主要用于液晶屏的显示控制、掉电数据保存,以及复杂的数学运算。系统工作原理框图如图1所示。

3 正交脉冲信号采集处理

3.1 正交脉冲采集

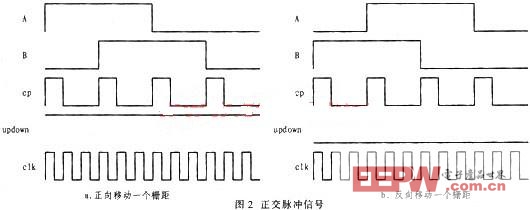

光栅尺输出一组正交脉冲信号,即相位差为90°的两路方波,如图2所示。当光栅尺正向移动一个栅距时,光栅尺输出一个00-01-11-10-00循环,A路方波相位超前于B路90°;当光栅尺反向移动一个栅距时,光栅传感器输出一个00-10-11-01-00循环,A路方波相位滞后B路90°。

分析A,B两路方波的逻辑状态发现A,B两路方波在任意时刻下只有一路信号发生逻辑状态变化。如果在逻辑状态变化前A,B两路的状态相同,那么变化后的逻辑状态肯定相异;如果变化前A,B两路方波逻辑状态相异,那么变化后逻辑状态肯定相同。只需对这两路信号异或,就能提取光栅尺运动的方向信号updown以及与运动距离成正比的计数脉冲cp。

由图2看出,光栅尺移动一个栅距将输出4个cp脉冲,系统测量的最小分辨率提高至1/4栅距,通常称为四裂相或四倍频。CPLD在每个clk的上升沿检测A,B两路方波的状态,首先分别对当前检测的状态A0,B0和上次检测的状态A1,B1相异或,然后将两次异或值再异或。如果最后异或值为1,则说明A,B两路方波发生变化,则向可逆计数器输入一个高电平宽度为1个clk周期的计数脉冲cp,实现逻辑如图3所示。

3.2 可逆计数器

将提取的方向信号updown和计数脉冲cp输入至可逆计数器,实现对光栅尺输出的正交脉冲计数。可逆计数器模块的VHDL程序如下:

3.3 clk的取值

由于CPLD的采样时钟clk必须大于8倍光栅尺输出的正交脉冲,因此系统不会丢失信号。该系统设计使用40 MHz有源晶体振荡器作为CPLD的采样时钟源,可记录的最大光栅传感器输出信号频率为5 MHz。如果使用50线/mm的光栅尺,经过CPLD的四裂相细分后,计算该光栅尺接该系统的最大不漏数加工速度为20 μm×5 MHz=100 m/s,最小分辨率为5μm。远远超出机床运行的极限速度,完全满足实际需求。

3.4 EPM240简介

选用Altera公司的 EPM240作为CPLD,EPM240是MAX II系列器件中的一员。MAX II CPLD系列的体系结构使其在所有CPLD系列器件的单位I/O引脚的功耗和成本最低;支持高达300 MHz的内部时钟频率,面向通用低密度逻辑应用,MAX II CPLD可替代高功耗和高成本ASSP以及标准逻辑CPLD。

EPM240含有240个逻辑单元(LE),等效于192个宏单元;8 192 bit的用户Flash存储器,可满足用户小容量信息存储要求;最大用户I/O数为80,最快速度为4.5 ns,完全满足系统设计要求。

4 MCU掉电数据存储

掉电数据存储是系统设计的另一重要功能,要求高可靠性。系统在掉电时应保存光栅尺的当前位置信息,下次开机时通过调用上次掉电时保存的位置信息恢复系统。因此,掉电瞬间,掉电报警电路将迅速响应,向MCU发出报警信号;MCU检测到报警信号后,马上进行相应处理,将当时光栅尺的当前位置信息存入EEPROM。其硬件电路如图4所示。

光栅 正交脉冲 掉电数据存储 CPLD EPM240 STC89C516RD 相关文章:

- 一种裸眼3D电视系统的设计方案* (10-27)

- 单片机AT89S51光栅系统在机床改造中的应用(01-16)

- 光纤光栅传感器的应用(10-15)

- 基于CAN通信的电源监控系统的设计(04-06)

- TPS54350在信号处理系统中的应用(06-09)

- 基于TPS759XX 多片信号处理系统的电源设计(07-29)