TPS54350在信号处理系统中的应用

时间:06-09

来源:互联网

点击:

DC/DC转换器TPS54350可在信号处理系统中提供多个电压,具有灵活、高效、紧凑等特点。

TPS54350是具有内部MOSFET的高效DC/DC转换器,连续输出电流为3A时,支持输入电压范围为4.5~20V,可使设计人员直接通过中压总线(而非依赖额外的低电压总线)为DSP、FPGA和微处理器供电。

特性和功能

TPS54350的输入电压为4.5~20V,输出电压可调低至0.891V,PWM频率固定为250kHz、500kHz或250~700kHz的可调节范围,还具有完善的保护功能。

TPS54350的管脚功能如下。

● VIN:电压输入引脚,必须旁路接一个低差错秒比率(ESR)为10μF的陶瓷电容;

● UVLO :低电压锁定输出;

● PWRGD:开沟道输出。引脚为低时,表示输出低于期望的输出电压值。PWRGD比较器的输出端有一个内部的上升沿滤波器;

● RT:频率设置引脚。在RT引脚与地(AGND)之间接一个电阻器来设置转换频率。将RT引脚与地连或是悬空,可以来得到一个内部的备选频率;

● SYNC:双向IO同步引脚。当RT引脚悬空或置低时,SYNC为输出;当它与一个下降沿信号连接时,亦可作为一个输入端口来同步系统时钟;

● ENA:使能引脚。低于0.5V时,芯片停止工作;悬空时被使能;

● COMP:误差放大器输出;

● VSENSE:误差放大器转换节点,基准电压值;

● AGND:模拟地,内部与感应模拟地电路连接。与PGND和PowerPAD连接;

● PGND:电源地,与AGND和PowerPAD连接;

● VBIAS:内部8.0V偏置电压。引脚要接一个0.1μF的陶瓷电容;

● PH:相位,与外部L-C滤波器连接;

● BOOT:在BOOT引脚与PH引脚之间连接一个0.1μF的陶瓷电容。

图1是TPS54350的实际应用电路图,图中给出的是其中的一种情况,其输出电压是可变的,通过改变电阻R2的值,来得到期望的输出电压值。图中的输入电压为12V,输出电压为3.3V,其中R2的计算公式为 R2 = R1 x 0.891/(Vo - 0.891),此时的R2阻值为374Ω,R1=1kΩ。

表1中给出当R1=1kΩ和R1=10kΩ时的几种输出电压之下的R2的值。本文所设计的系统中,就是运用图1所示的电路来实现的。根据不同的输出电压要求,赋给R2不同的阻值,其阻值的取法可参照表1。另外,对于一个设计者来说,在设计电路时要考虑到以下几个因素,见表2。本系统中的R1阻值为1kΩ。

在信号处理系统中的应用

本信号处理系统采用的是ADI公司的ADSP TS101s芯片所组成的多片某仿真雷达信号处理系统,系统主要由五片DSP、一片CPLD和七片TPS54350组成。在以往使用MAX1951的经验基础上,经过多方面的设计考虑,系统采用了TPS54350芯片。从表1可以看出,TPS54350可以输出3.3V和1.2V的电压。系统中的DSP采用的是240MHz的时钟,每个指令周期约为4.17ns。根据ADSP TS101s的操作条件可知,当温度为25℃,时钟CCLK为250MHz时,典型情况下的VDD(1.25V)供电电流的典型值为1.2A,VDD_IO的供电电流小于137mA。TPS54350的额定输出电压为3A,所以此系统的设计是合理的。

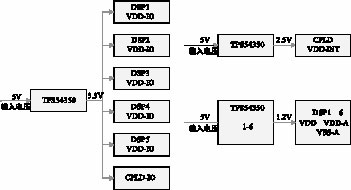

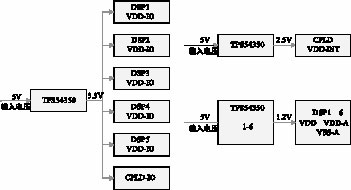

TigerSharc DSP有三个电源,其中数字3.3V(VDD_IO)为I/O供电;数字1.2V(VDD)为DSP内核供电;模拟1.2V(V)为内部锁相环和倍频电路供电。系统将主机送来的5V经过TPS54350得到3.3V和1.2V的电压。各片DSP的数字1.2V(VDD_A)电源各由一片TPS54350供给。五片DSP内部模块1.2V(VDD_A)由同一DSP芯片的VDD(+1.2V)经滤波网络后解决。五片DSP的I/O 3.3V电源直接由主机送来的5V经过TPS54350得到的3.3V统一供给,同时也提供CPLD(EP1k30)的VCC_IO(+3.3V)的电压。其中CPLD的VCC_INT(+2.5V)利用TPS54350输出的+2.5V的电压来供电。本文给出了系统的供电框图,如图2所示。图3中给出了单片DSP的内核供电框图及外围电路配置。

TPS54350采用的是小型16引脚HTSSOP封装。根据以往的经验,建议设计者在设计PCB时,最好给TRS54350加上散热片,电源线尽量粗。在TPS54350的前后均加上了滤波网络,尽量保证得到比较合适的电压。

系统中的EP1K30产生上电复位波形和时序控制。由于EP1K30需要一个配置芯片,而且它和DSP存在一个上电先后的问题。也就是说,在上电后,如果CPLD芯片完成配置文件的读入时,DSP仍未上电稳定,则应充分延长Tstart_IO的低电平时间,以避免DSP上电未稳定而CPLD上电波形已结束。因此,应保证DSP上电稳定先于CPLD芯片配置文件的读入,此问题在系统设计时应予以充分重视,否则DSP将无法正常工作。TigerSharc DSP要求数字3.3V和1.2V应同时上电。若无法严格同步,则应保证内核电源1.2V先上电,I/O电源3.3V后上电。本系统在数字3.3V输入端并联了一个大电容,而在数字1.2V输入端并联了一个小电容,其目的就是为了保证3.3V充电时间大于1.2V充电时间,以便很好地解决电源供电先后的问题。

TPS54350是具有内部MOSFET的高效DC/DC转换器,连续输出电流为3A时,支持输入电压范围为4.5~20V,可使设计人员直接通过中压总线(而非依赖额外的低电压总线)为DSP、FPGA和微处理器供电。

特性和功能

TPS54350的输入电压为4.5~20V,输出电压可调低至0.891V,PWM频率固定为250kHz、500kHz或250~700kHz的可调节范围,还具有完善的保护功能。

TPS54350的管脚功能如下。

● VIN:电压输入引脚,必须旁路接一个低差错秒比率(ESR)为10μF的陶瓷电容;

● UVLO :低电压锁定输出;

● PWRGD:开沟道输出。引脚为低时,表示输出低于期望的输出电压值。PWRGD比较器的输出端有一个内部的上升沿滤波器;

● RT:频率设置引脚。在RT引脚与地(AGND)之间接一个电阻器来设置转换频率。将RT引脚与地连或是悬空,可以来得到一个内部的备选频率;

● SYNC:双向IO同步引脚。当RT引脚悬空或置低时,SYNC为输出;当它与一个下降沿信号连接时,亦可作为一个输入端口来同步系统时钟;

● ENA:使能引脚。低于0.5V时,芯片停止工作;悬空时被使能;

● COMP:误差放大器输出;

● VSENSE:误差放大器转换节点,基准电压值;

● AGND:模拟地,内部与感应模拟地电路连接。与PGND和PowerPAD连接;

● PGND:电源地,与AGND和PowerPAD连接;

● VBIAS:内部8.0V偏置电压。引脚要接一个0.1μF的陶瓷电容;

● PH:相位,与外部L-C滤波器连接;

● BOOT:在BOOT引脚与PH引脚之间连接一个0.1μF的陶瓷电容。

图1是TPS54350的实际应用电路图,图中给出的是其中的一种情况,其输出电压是可变的,通过改变电阻R2的值,来得到期望的输出电压值。图中的输入电压为12V,输出电压为3.3V,其中R2的计算公式为 R2 = R1 x 0.891/(Vo - 0.891),此时的R2阻值为374Ω,R1=1kΩ。

表1中给出当R1=1kΩ和R1=10kΩ时的几种输出电压之下的R2的值。本文所设计的系统中,就是运用图1所示的电路来实现的。根据不同的输出电压要求,赋给R2不同的阻值,其阻值的取法可参照表1。另外,对于一个设计者来说,在设计电路时要考虑到以下几个因素,见表2。本系统中的R1阻值为1kΩ。

在信号处理系统中的应用

本信号处理系统采用的是ADI公司的ADSP TS101s芯片所组成的多片某仿真雷达信号处理系统,系统主要由五片DSP、一片CPLD和七片TPS54350组成。在以往使用MAX1951的经验基础上,经过多方面的设计考虑,系统采用了TPS54350芯片。从表1可以看出,TPS54350可以输出3.3V和1.2V的电压。系统中的DSP采用的是240MHz的时钟,每个指令周期约为4.17ns。根据ADSP TS101s的操作条件可知,当温度为25℃,时钟CCLK为250MHz时,典型情况下的VDD(1.25V)供电电流的典型值为1.2A,VDD_IO的供电电流小于137mA。TPS54350的额定输出电压为3A,所以此系统的设计是合理的。

TigerSharc DSP有三个电源,其中数字3.3V(VDD_IO)为I/O供电;数字1.2V(VDD)为DSP内核供电;模拟1.2V(V)为内部锁相环和倍频电路供电。系统将主机送来的5V经过TPS54350得到3.3V和1.2V的电压。各片DSP的数字1.2V(VDD_A)电源各由一片TPS54350供给。五片DSP内部模块1.2V(VDD_A)由同一DSP芯片的VDD(+1.2V)经滤波网络后解决。五片DSP的I/O 3.3V电源直接由主机送来的5V经过TPS54350得到的3.3V统一供给,同时也提供CPLD(EP1k30)的VCC_IO(+3.3V)的电压。其中CPLD的VCC_INT(+2.5V)利用TPS54350输出的+2.5V的电压来供电。本文给出了系统的供电框图,如图2所示。图3中给出了单片DSP的内核供电框图及外围电路配置。

TPS54350采用的是小型16引脚HTSSOP封装。根据以往的经验,建议设计者在设计PCB时,最好给TRS54350加上散热片,电源线尽量粗。在TPS54350的前后均加上了滤波网络,尽量保证得到比较合适的电压。

系统中的EP1K30产生上电复位波形和时序控制。由于EP1K30需要一个配置芯片,而且它和DSP存在一个上电先后的问题。也就是说,在上电后,如果CPLD芯片完成配置文件的读入时,DSP仍未上电稳定,则应充分延长Tstart_IO的低电平时间,以避免DSP上电未稳定而CPLD上电波形已结束。因此,应保证DSP上电稳定先于CPLD芯片配置文件的读入,此问题在系统设计时应予以充分重视,否则DSP将无法正常工作。TigerSharc DSP要求数字3.3V和1.2V应同时上电。若无法严格同步,则应保证内核电源1.2V先上电,I/O电源3.3V后上电。本系统在数字3.3V输入端并联了一个大电容,而在数字1.2V输入端并联了一个小电容,其目的就是为了保证3.3V充电时间大于1.2V充电时间,以便很好地解决电源供电先后的问题。

电压 MOSFET 电流 总线 DSP FPGA PWM 电容 比较器 滤波器 电阻 放大器 电路 电路图 ADI 仿真 CPLD PCB 电子 相关文章:

- 用于电压或电流调节的新调节器架构(07-19)

- 超低静态电流电源管理IC延长便携应用工作时间(04-14)

- 电源设计小贴士 2:驾驭噪声电源(01-01)

- 负载点降压稳压器及其稳定性检查方法(07-19)

- 电源设计小贴士 3:阻尼输入滤波器(第一部分)(01-16)

- 高效地驱动LED(04-23)