简易USB与LVDS接口转换器

1 引言

通用串行总线USB(Universal Serial Bus)接口以其通信速率快,USB2.0协议速率达480 Mb/s,支持热插拔的特点得到广泛应用,缓解日益增加的PC外设与有限的主板插槽和端口之间的矛盾;而低压差分信号LVDS(Low-Voltage Differential Signaling)接口作为一种新型的高速串行。低噪声的数据传输接口,广泛应用于视频传输领域,实现USB与LVDS接口转换,使在只有USB接的情况下便可实现双视频显示的连接,进一步扩展两种接口的使用范围,从而在一定程度上解决主板插槽与端口日益匮乏的问题。

2 系统概述

该系统设计主要由稳压电路,USB接口,基于FPGA的协议数据转换以及LVDS接口等部分组成,其系统设计框图如图1所示。该系统设计的USB接口使用高速USB物理层收发器USB3300将USB协议的差分信号转换成8位的并行信号后,再与FPGA交互数据,从而避免FPGA直接与USB协议的物理层交互数据,简化FPGA可编程门阵列编程。基于同样思想,系统LVDS接口部分采用SN65LV1023与SN62LV1224,将低压差分信号转换成 10位的并行信号再与FPGA进行数据交互。通过专用转换器USB3300,SN65LV1023,SN65LV1224使得FPGA只与并行信号和相应的控制信号连接,而不与USB协议和LVDS协议的复杂物理层信号交互,从而较为简单地实现协议数据转换的软件编程。

系统设计使用两片USB3300,其中USB3300 A与主机PC的USB接口相连,将主机传输的USB协议数据转换后,通过与FPGA的数据交互以及FPGA的协议数据转换,转换成10位并行信号,输出给 SN65LV1023,最后以LVDS协议的低压差分信号输出,实现USB接口到LVDS接口的转换。而SN65LV1224与主机的LVDS接口连接,将LVDS协议的数据转换成10位并行输入FPGA进行协议数据转换后,再将8位并行数据与USB3300_B进行数据交互,最后以USB协议的差分信号输出,从而实现LVDS接口到USB接口的转换。

3 系统硬件设计

3.1 稳压电路

该系统设计需要提供5 V和3.3 V的稳定电压信号。于是稳压电路部分使用TPS76815向系统提供5 V的电压信号,TPS76815电路连接如图2所示,使能丽引脚接地,为除去毛刺则在OUT端接4.7μF和0.01μF的电容滤波,使用 TPS76833提供3.3 V电压信号。TPS76833连接电路与TP$76815类似。

3.2 USB接口电路

因为USB协议的物理层定义过于复杂,采用FPGA现场可编程逻辑门阵列与USB协议物理层交互难度太大,同时也很难满足数据收发时序同步要求。所以应在与FPGA数据交互前进行必要的数据转换。因此,考虑使用USB控制器。而一般的 USB控制器只支持USB1.1协议,并不满足高速传输要求.而转换后的数据也较复杂。不利于协议数据转换部分的编程。本系统应用SMSC公司开发的高速 USB物理层收发器USB3300。USB3300使用低引脚计数接口(ULPI)连接ULPI兼容链路层。ULPI接口在链路层和PHY之间采用传输频带内信号和状态字节的方法,将引脚数从UTMI+接口的54降低到12。这样大大降低USB协议物理层与FPGA数据交互的难度,易于软件编程。

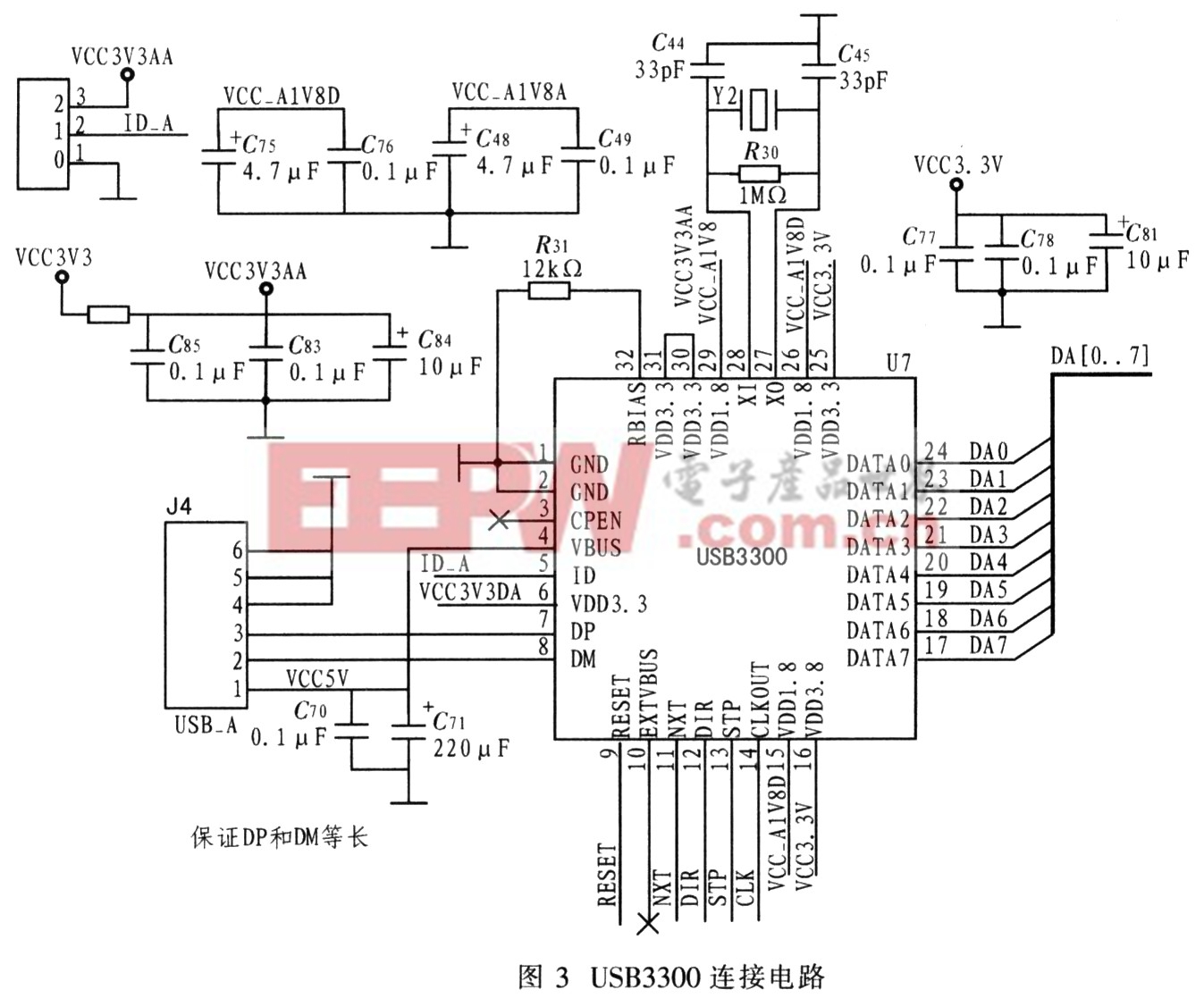

USB3300连接电路如图3所示,为控制数据传输的时序同步,采用USB3300的时钟输出工作方式。USB3300外接24 MHz的时钟晶体振荡器,经内部锁相环电路转换为60 MHz信号,通过CLK输入FPGA作为其时钟信号,从而实现FPGA与USB3300的时钟同步。USB接口部分与FPGA的数据交互传输通过双向的8 位数据信号实现,USB3300通过DIR与NXT信号输出控制数据信号的传输方向,而FPGA通过STP信号控制数据的传输方向USB3300的状态。这样便实现FPGA与USB3300的数据交互。

3.3 协议数据转换部分

系统协议数据转换部分中采用现场可编程逻辑门阵列器件EP1C6U240C8进行编程,主要实现的功能是将与USB3300交互的数据转换成10位并行数据与SN65LV1023和SN65LV1224交互,同时通过STP信号控制 USB3300的数据传输方向和USB3300的状态。由于USB协议本身有低功耗模式,在低功耗模式时锁相环关闭,在硬件设计时一定要接RESET控制键,这样便于软件编程的调试。

3.4 LVDS接口电路

低压差分信号LVDS(Low Voltage Differential Signaling)接口是一种高速数据传输的物理层接口,其电压信号摆幅低,技术上能做到且产生极低噪声,功耗也极低,主要用于服务器、可堆垒集线器、无线基站、3FG交换机及高分辨率显示等。与USB协议接口类似其物理层信号直接与FPGA进行交互相当复杂,系统选用SN65LV1224和 SNLV1023,将FPGA与LVDS接口物理层数据交互,转换为10位的并行信号,同时通过相关的控制信号控制数据的传输方向。SN65LV1023 与SN65LV1224的硬件连接电路分别如图4和图5所示,其中SN65LV1023实现10位并行数据转换成LVDS的低压差分信号,同时FPGA通过TCLK_R/F控制内部锁相环,进而控制SN65LV1023状态。而SN65LV1224则将LVDS的低压差分信号转换成10位并行数据信号输入 FPGA,这样通过SN65LV1023与SN65LV1224,便在较为简单的情况下实现FPGA与LVDS接口的数据交互。

转换器 接口 LVDS USB 简易 USB,低功耗 相关文章:

- 1200V CoolSiCTM MOSFET兼具高性能与高可靠性(06-28)

- 如何借用同步整流架构提高电源转换器效率(12-09)

- 高端准谐振零压开关反激式转换器中的ESBT技术(12-09)

- A→D 转换器的保真度测试(12-09)

- 如何通过配置负载点转换器 (POL) 提供负电压或隔离输出电压(12-09)

- 基于LNK302/LNK304-306离线转换器的非隔离电源及恒流LED驱动器(12-08)