eGaN FET比拼MOSFET,驱动器和布局

通。虽然增加栅极驱动吸收电阻有助于抑制这种LCR谐振,代价是增加了米勒导通敏感度,如果加入于谐振频率点具有电阻特性(损耗)的铁氧体磁珠,我们可以取得相同效果,其米勒导通敏感度也不会增加那么多。请参考图5的等效电路和图6所示的概念性开关波形。这种效应有时很难与dV/dt导致的米勒导通区分。总而言之,CSI对于eGaN FET的重要性要比对于硅器件的重要性高得多,因为其具有更高的di/dt和dV/dt,应该通过仔细的布局设计,把它们减小到最低限度。

建议的布局

根据上述不同考虑因素,我们可以开发一些推荐的布局。这里的布局表示的是一种半桥配置,但遵循上述要求也可以扩展到其他应用。

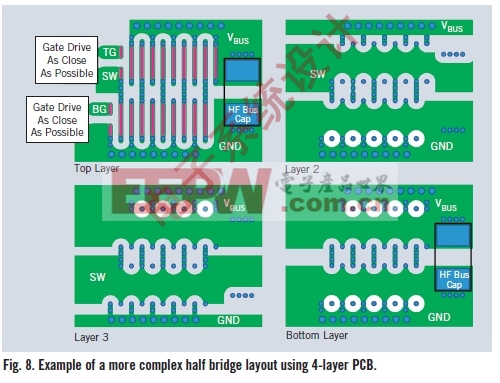

图7和图8分别显示了简单和复杂的4层PCB。值得注意的是,我们需要尽量增加铜厚度,以限制电阻性损耗及改善散热性能(我们推荐的外层铜厚度为2盎司)。在这两个布局例子中,每个器件的源极连接都是从底下引出来,具有屏蔽功能,可以最大限度地减少额外的寄生CGD。在较简单的布局(图7)中,栅极返回连接做在较小的源极栅极焊盘上,可分离栅极返回电流和源极中的器件漏极电流路径,从而最大限度地减少CSI。

在图8所示的更复杂的设计中,我们则进一步将每个源极连接,通过第二层连接到现在的双屏蔽层,作为栅极驱动返回路径。漏极连接同样在第三层上引出。我们需要折衷的是,要想达到更低的CSI和整体环路/布局电感,几何结构需要增加寄生电容——特别是CDS(输出电容)——这是因为我们仍然需要最大限度地减小栅极到漏极的寄生电容。

散热考虑

由于本质上eGaN具有更低的导通电阻,这些器件的尺寸比具有同等导通电阻的功率MOSFET裸片小很多,因此具有高得多的等效热阻。然而,eGaN FET还具有低得多的FOM,因此具有较低的开关功率损耗。

这种功率损耗方面的改进可以补偿更高的热阻吗?为了回答这个问题,我们需要了解两种常见情形:(1)器件作为“倒装芯片”安装在印制电路板上,没有额外的散热器;(2)器件采用双面冷却方式安装。

单面冷却:

因为eGaN FET构建在标准硅晶圆上面的非常薄的异质结材料层上,因此这些器件直接安装在PCB上,由于没有任何背面冷却器件,其散热表现与相似装贴的硅器件不一样。需要完全了解的影响热性能表现结果的变量包括:(1)PCB铜箔面积;(2)铜厚度;(3)PCB材料;以及(4)器件周围的空气流通情况。

参考文献[6]测试了直接安装在FR-4 PCB材料上的多个行业标准封装。测量对象是1平方英寸、2盎司铜、具有足够铜及电气接触引线的器件。这种方法将器件外形的影响与PCB上铜所带来的冷却效果分隔。当不同封装被安装在一平方英寸的铜上面时(D2PAK封装的最小RTHJA为18℃/W,SO-8的最大RTHJA为34℃/W),我们看到的影响相对较小的。这是因为主要的热阻因素是透过PCB散热。与这些测试一致的是,据宜普公司估计,安装在一平方英寸、2盎司铜上的eGaN FET的RTHJA在静止空气中应该大约是40℃/W。这个性能可以通过增加空气流通而得以显著改善。

双面冷却:

为了确定宜普eGaN FET的最佳顶层冷却效果,我们构建了如图9所示的装置。针对这些“最佳案例”的热测量,我们将RDS(ON)用作温度灵敏度参数,而散热器经过水冷过程。根据宜普对eGaN FET一系列产品的测量数据表明,当冷却主要通过eGaN FET有效面积下方的硅基底进行时,其数据是12-14℃-mm2的标准化RTHJA。在这些条件下,宜普的大面积eGaN FET具有约2℃/W的RTHJA,小面积FET则具有约8℃/W的RTHJA。

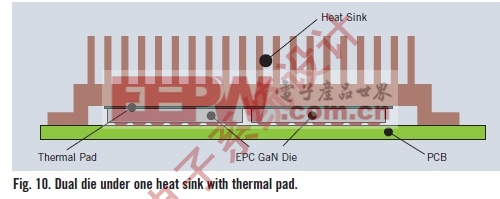

实际上,可实现的双面冷却当然没有图9所示的那么优秀,还会导致最终热阻更高。在图10所示的配置中,两个器件由一个散热器同时冷却。这里多个裸片被放置在同一散热器下方。但是这样做必须十分小心,避免因为裸片稍微倾斜或距离PCB不同高度所引起的不均匀压力,继而造成机械性损坏。如3M、Dow Corning或BeRGquist产品等热传导材料已被成功采用,能够双面冷却散热器下方的多个裸片。

为了充分发挥宜普eGaN FET的全部优势,设计师必须理解如何设计在具有成本效益的PCB上工作的高成本效益驱动电路。在Shootout系列中的第一篇论文中,我们讨论了重要的品质因数(FOM),它可以帮助设计师预测在各种广泛应用中的产品性能。在本文中,我们讨论了栅极驱动要求、布局和热设计需要考虑的各种因素,这些因素对想要开发能够充分发挥eGaN FET优势的产品的设计师来说都很重要。

本系列的下一篇文章将讨论基于eGaN FET的以太网供电(POE)设计,这些设计的功率密度要比使用先进的功率MOSFET设计的类似电路高得多。

eGaN FETMOSFET 硅功率产品 驱动器 相关文章:

- eGaN FET与硅器件比拼之低功率无线电源转换器(12-09)

- 差分运算放大器驱动器实现高分辨率ADC输入过压保护(03-23)

- 用集成式8开关无闪烁驱动器控制矩阵式LED前灯中的单个LED(下)(03-24)

- 基于1602液晶电压驱动器应用于proteus仿真(12-12)

- 用集成式8开关无闪烁驱动器控制矩阵式LED前灯中的单个LED(上)(03-23)

- 三相PWM电机驱动器A3936及其应用[图](12-09)