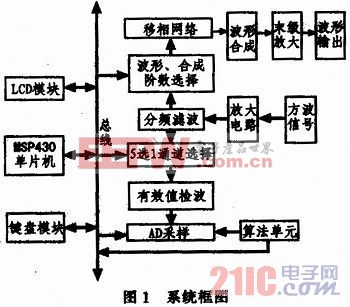

基于MSP430F499的波形合成器

3.1 整个系统中电源的去耦问题

在整个系统中会用到很多的运算放大器芯片。一般来说,运算放大器的供电电源端应连接去耦电容(对交流放大器尤其需要),以消除信号电流通过电源内阻给电路带来的影响。运算放大器的性能不同,其去耦电容的容量也有所不同。对于低速运算放大器,一般在紧靠运放供电端与电源地之间接容量为0.1μF的电容就可以了,但是对于高速运算放大器,应当在紧靠运放的供电端与电源地之间用容量为10μF和容量为0.01μF的电容器并联连接。整个系统中所有的运算放大器都做了去耦处理,只是画图中为简单起见,省略了去耦电容。

除此之外,运算放大器的地线连接也有讲究,对于小功率运放而言,地线连接无特殊要求,但对于较大功率的运算放大器,地线连接相当重要。总的原则是地线应短而粗并且在同一点连接。本系统中数字地模拟地共存,因此设计时将所有模拟地和数字地分别连接,最后电路中的模拟地和数字地与电源地一点汇集。

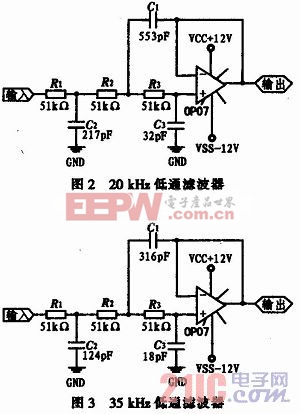

3.2 滤波电路

图2、图3中两个低通滤波器都是三阶巴特沃斯低通滤波器。有源滤波器适应在低频段(100 kHz)的滤波,当频率较低时,若用无源滤波,电容、电感的元件值及体积都会很大,大电容电感不易获得,且误差较大,而有源滤波器则可以依靠运放在低频段的诸多优势(尤其是低噪声运放)达到很好的滤波效果。10 kHz、30 kHz、50 kHz信号经八阶椭圆开关电容滤波器滤波后,10 kHz、30 kHz、50 kHz信号再分别用理论截止频率为20kHz、35 kHz、55 kHz的低通滤波器滤波,理论值与实际截止频率有一定的偏差,为防止有用信号落在通频带之外,理论截止频率没有按照严格的10kHz和30kHz。

3.3 移相电路

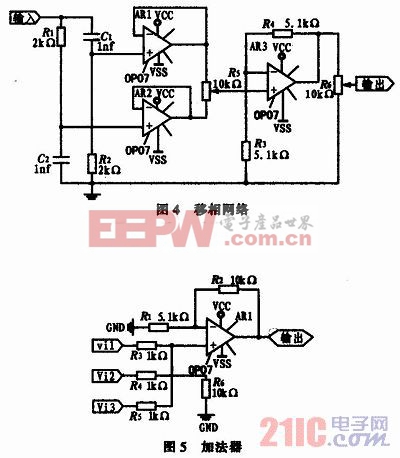

RC移相网络参数的计算:

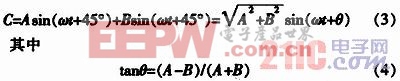

要求叠加后的信号移相范围为-45°~+45°,设A信号为Asin(ωt+45°),B信号为Bsin(ωt+45°),叠加后的信号为

改变A和B的值就可以改变叠加后信号的相位。

只有输入信号的频率与RC网络的谐振频率相同时,才会有45°的相移,因此随着输入信号频率的变化,RC网络的谐振频率也要相应的改变。根据公式

f=1/2πRC (5)

推导可得R值,取电容C为0.1μF,当输入信号的频率为100Hz时,R=16kΩ,当频率为1kHz时,R=1.6kΩ,当频率变为10kHz时,R=160Ω。

输入的正弦信号经过RC构成的超前和滞后网络后经过运放(OPA37)构成的射极跟随器,然后通过电位器R3叠加,再经过放大电路通过一个电位器输出。电路图如图4所示。

3.4 加法器

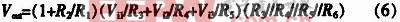

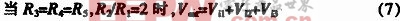

此加法器为同相加法器,由于集成运放可视为理想运放,其输入端可视为虚短和虚开路。在同向端运用节点电流方程可求得输出:

3.5 有效值检波

有效值检波采用真有效值/直流转换芯片AD637能计算任何复杂波形的真有效值、平均值、均方值、绝对值,具有分贝输出(0~60 dB)。具有宽频带,量程在0~7 V范围内可调。

AD637内部结构包括有源整流器(即绝对值电路),平方/除法器、滤波放大器、独立的缓冲放大器、偏置电路五部分。使用AD637在测量峰值系数高达10的信号时附加误差仅为1%,且外围元件少、频带宽。对于有效值为200 mV的信号,-3dB带宽为600kHz;对于有效值为1V的信号。-3dB带宽为8MHz。该方案硬件简单,两且精度很高,效果理想。

4 系统软件设计

软件流程图见图6,本系统选用MSP430F449单片机,主要负责对方波、三角波10k、30k、50k等各次谐波连行采样,并用LCD12864对各次谐波的峰值显示;在程序运行的过程中,可通过16x16矩阵键盘控制选择波形及阶数的切换。

合成器 波形 MSP430F499 基于 相关文章:

- 基于高电压电荷泵的PLL频率合成器设计(01-15)

- 一种X波段频率合成器的设计方案(08-07)

- 宽带低相噪高分辨率频率合成器设计(06-27)

- saber仿真中波形计算器的详细使用(12-09)

- 逆变电源的SPWM波形发生电路(12-08)

- 跟电源专家陶显芳学电源技术(二):漏感与分布电容对输出波形的影响(下)(12-16)