宽带低相噪高分辨率频率合成器设计

摘要 利用锁相环(PLL)和YTO相结合,设计出一种频率合成器。实现了3~7 GHz的频率覆盖和低于0.2 Hz的频率分辨率。全频段相噪均在-108 dRc/Hz@10 kHz以下,具有较高的实用价值。

关键词 频率合成器;锁相环;DDS;YTO

在微波领域,频率合成器是构成测量仪器的核心器件。高性能的测量仪器需要具备大带宽、高分辨率和低相位噪声。而传统的压控振荡器(Voltage Controlled Oscillator,VCO)是窄带器件,不能满足宽频段、低相噪的要求。由于YIG调谐振荡器(TIG Tuned Oscillators,YTO)具有宽频率范围、良好的低相位噪声和线性调谐等方面的优势而成为频率合成器的首选器件。

1 方案设计

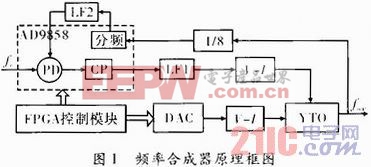

设计选用中国电子科技集团第41研究所研制的YIG调谐振荡器(YTO)产生3~7 GHz的输出频率。利用美国Analog Devices公司生产的高速直接频率合成器的DDS芯片AD9858实现小数分频,产生频率的微步进。原理框图如图1所示。

YTO振荡器输出3~7 GHz的频率经8分频后作为AD9858的参考时钟。经分频、滤波后与100 MHz参考频率fr进行鉴相,这里鉴相器用的是AD9858内部集成的鉴相器,鉴相器输出的是电流信息,它由内部集成的可编程快锁充电泵(CP)提供,这个电流不能直接驱动YTO,所以经过二阶的无源环路滤波器转换成误差电压,经YTO驱动电路后控制YTO调频线圈,来锁定YTO的频率。

2 关键电路设计

2.1 YTO驱动电路设计

YTO内部的调谐磁场由主线圈和副线圈两部分组成,前者感抗大、调谐慢,但调谐灵敏度高、调谐范围宽、高频干扰抑制好;后者感抗小从而调谐范围窄,但调谐速度快,并因为调谐灵敏度低而具有良好的干扰抑制特性。二者结合使用既可以实现大范围的调谐,又可以获得较快的频率跟踪性能。

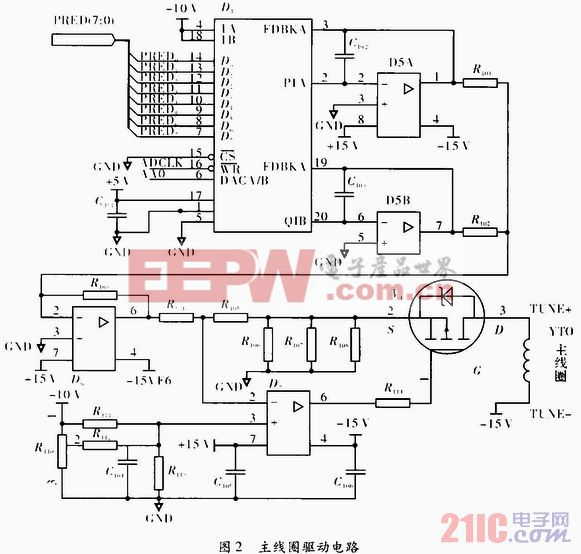

主线圈驱动电路设计如图2所示,这部分电路是在锁相环路之外,有助于实现频率合成器的快速锁定,为精确调谐YTO主线圈,这里选用的是ADI公司的AD7528双8位DAC(D4),直接接受FPGA的并口数据控制(PRED0~PRED7),实现16位预置数送数的目的。AA0为低时送高8位预置数,AA0高为时送低8位预置数,运放TL072ACD完成了ADC的输出电流到电压的转换。经由R101、R102、R103和D6,其中R102=256R101组成的加法电路将两路电压相加。D/A送数改变MOS管IRF9520的G极、S极电压值,VGS电压差随着DA预置数增大而增大,VGS增大使D极电流ID变大,

MOS管IRF9520的D极直接与YT0主线圈相连,从而改变了流经YTO主线圈的电流值,达到调谐的目的。

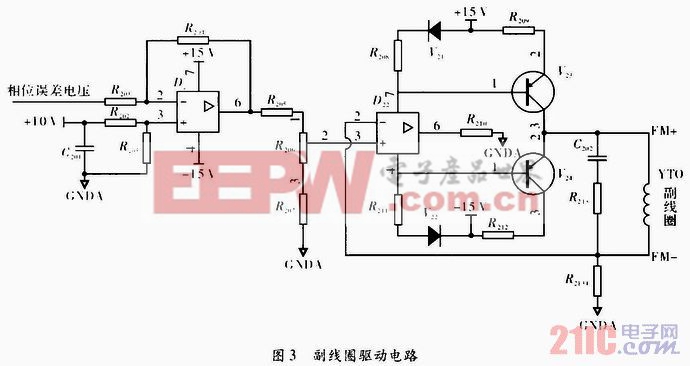

副线圈驱动电路设计如图3所示,为得到调频端合适的驱动电流和适应调频端的电流正、负偏,设计了一种驱动电路如图3所示。正的相位误差电压经带偏移的差分放大电路转变成正或负的电压,D22的3脚从变阻器R206的2脚获得相应的正或负的电压。文中使用的YTO调频端的调谐 灵敏度是300 kHz/mA,通过调节变阻器R206的2脚位置将环路捕捉带宽设定约为30 MHz。利用运算放大器D22两个电压输入脚的等电位特性来获得YTO调频线圈的驱动电流。当D22的3脚输入电压为正时,V23导通,电流从YTO的FM+端到FM-端。反之,当D22的3脚输入电压为负时,V24导通,电流从YTO的FM-端到FM+端。

2.2 小数分频电路设计

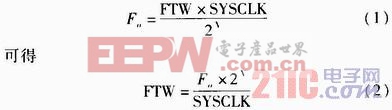

直接数字频率合成(DDS)作为新一代频率合成技术,具有输出频率分辨率高、频率切换速度快、相位变化连续以及数字可控等优点。采用小数分频在不降低鉴相频率的前提下,可以提高频率分辨率。本方案利用DDS芯片AD9858实现小数分频。AD9858内部集成有10位数模转换器,其频率分辨率为32位。根据公式

式中,FTW表示DDS频率控制字;F0表示DDS输出频率;N表示DDS频率控制字的位长;SYSCLK表示DDS参考时钟;YTO振荡器输出3~7 GHz的频率经8分频为375~875 MHz作为AD9858的参考时钟。方案要求AD9858输出频率F0始终为100 MHz,根据式(2)可以计算出频率控制字FTW,由FPGA通过并行送给AD9858。由AD9858分频输出100MHz频率经低通滤波器后与100 MHz参考频率fr进行鉴相。根据式(1)可以计算出频率分辨率为0.09~0.2Hz。

2.3 环路滤波器设计

在锁相环路中,环路滤波器起着至关重要的作用,它将误差电流分量转化为误差电压分量,滤除误差电压中的高频分量和噪声,以保证环路所需要的性能,增加环路稳定性。在锁相环电路设计中,为达到优异的相位噪声,人们往往采用无源环路滤波器完成设计,设计时需要重点考虑带宽,相位裕度,滤波器结构、阶数、极点等参数。在本方案中由于相位误差电压在0~5 V之间,故选择无源滤波器,利用PLL DesignSimulation V4.0仿真软件设计出环路带宽200 kHz,相位裕度45°,阻尼系数0.707的二阶无源滤波器如图4所示。经实际调试后R1=2 kΩ,R2=39.2 Ω,C1=0.1μF,C2=11 nF。

- 基于高电压电荷泵的PLL频率合成器设计(01-15)

- 一种X波段频率合成器的设计方案(08-07)

- 基于MSP430F499的波形合成器(02-09)

- 3D IC设计打了死结?电源完整性分析僵局怎么破(09-21)

- 快速调试嵌入式MCU设计仿真的三大因素浅析(12-12)

- 访问电源参考设计库的众多理由(12-09)