一种X波段频率合成器的设计方案

摘要:在非相参雷达测试系统中,频率合成技术是其中的关键技术,针对雷达测试系统的要求,介绍了一种用DDS激励PLL的X波段频率合成器的设计方案。文中给出了主要的硬件选择及具体电路设计,通过对该频率合成器的相位噪声和捕获时间的分析,及对样机性能的测试,结果表明该X波段频率合成器带宽为800 MHz、输出相位噪声优于-80 dBc/Hz@10 kHz、频率分辨率达0.1 MHz,可满足雷达测试系统系统的要求。测试表明,该频率合成器能产生低相噪、高分辨率、高稳定度的X波段信号,具有较好的工程应用价值。

关键词:DDS;PLL;低相位噪声;环路滤波器

在非相参雷达测试系统中,频率合成技术是其中的关键技术之一,它要求在一个很宽的频率范围内以快捷的速度,提供大量的高精度、高分辨率、高稳定度的频率信号。频率合成的主要方法有直接频率合成、锁相频率合成(PLL)和数字直接频率合成(DDS)。PLL虽然有锁定频率高、带宽宽以及频谱质量好等优点,但是存在置频时间长、分辨率较低等缺点。DDS有频率分辨率高、频率转换时间快、输出相位噪声低等优良特性,但其输出频率低、杂散性能较差,这些因素又限制了它们的使用。如果把两者结合起来,取长补短,则可以获得更高的频率分辨率、更快的信号建立时间、低相噪和宽输出频率范围等性能。

1 X波段频率合成器的方案设计

常用的DDS+PLL组合有DDS激励PLL和DDS内插PLL 2种方式。无论采用哪种组合方式,都可以获得高分辨率、快速转换、较宽频率范围的输出频率。但在频率杂散性能、频率建立时间和电路复杂程度等方面,两种组合特点各有不同。在PLL内插DDS的组合方案中,虽然DDS输出不经PLL倍频,故具有较低的相位噪声和较好的杂散性能,但此方案需要滤除混频器产生的多余分量,影响环路参数,致使设计电路复杂,硬件调试周期长。而前者硬件结构简单易实现,系统稳定性高。

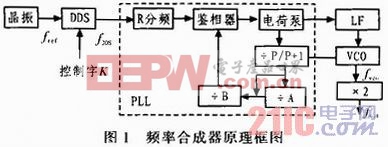

本方案采用DDS激励PLL的方式对X波段频率合成器进行设计。系统原理图如图1所示。

PLL由数字鉴相器、高精度电荷泵、可编程参考分频器R、可编程A,B计数器以及双模分频器(P/P+1)组成。当PLL锁定时,频率合成器及VCO输出频率为:

DDS的输出频率受频率控制字K控制,且![]()

式(3)中K为DDS的频率控制字,M为相位累加器字长,fCLK为DDS的内部工作频率。因此(1)式可以写为![]()

2 硬件电路设计

本设计用于实现X波段低相噪锁相频率源,其中心频率为9.4 GHz,带宽为800 MHz,频率分辨率为100 kHz,相位噪声要求为-80 dBc /Hz@10 kHz,由(1)式知VCO的输出频率为4.5~4.9 GHz。鉴于以上考虑,本方案采用DDS芯片AD9910和锁相芯片ADF4106对硬件电路进行了设计。

2.1 AD9910的性能特点

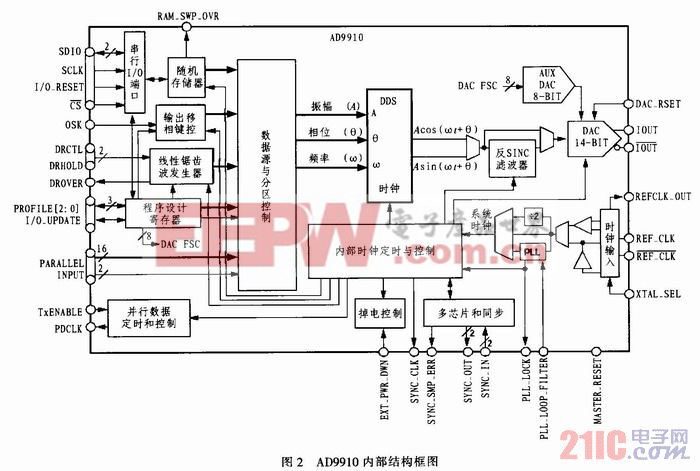

AD9910是ADI公司推出的一款直接数字频率合成器(DDS)芯片,与其他高速DDS器件相比,它集成14位数/模转换器(DAC),可以形成数字可编程、高频模拟输出的频率合成器,能够产生频率高400MHz的正弦波形。这款DDS使用32位累加器,可提供快速调频和频率调节分辨率。其采样率为1GSPS,调节分辨率为0.23 Hz。该DDS也支持快速的相位和幅度切换,具有PLL REFCLK乘法器。

AD9910可通过串行I/O端口设置内部控制寄存器内容,其内部包含静态RAM(1 024字x32位RAM)以支持多种频率、相位和幅度调制。AD99 10也支持用户定义、数字控制的线性扫描工作模式。

为了获得更高级的调制功能,其集成了高速并行数据输入端口以支持直接频率、相位、幅度或极性调制。AD9910可应用于捷变本振频率合成、快速跳频和雷达线性调频源中。

AD9910的电源电压为1.8 V和3.3 V,功率消耗为715~850 mW,具有软件和硬件控制的低功耗模式,低功耗模式的功耗为19~25 mW。其DAC输出相位噪声为-125 dBc/Hz@1 kHz,可进行25 Mb/s写速度串行I/O控制。AD9910的内部结构框图如图2所示。

2.2 ADF4106的性能特点

ADF4106是美国ADI公司生产的高性能锁相频率合成芯片,主要由数字鉴相器、电荷泵、R分频器、A,B计数器及双模前置P/P+1分频器等组成。数字鉴相器对R计数器与N计数器的输出信号进行相位比较,得到一个误差电压。14bit可编程参考R分频器对外部晶振分频后得到参考频率。该器件可以通过可编程6位A计数器、13位B计数器及双模前置分频器(P/P+1)来共同完成主分频比N(N=BP+A)。因此,设计时只需外加环路滤波器,并选择合适的参考值,即可获得稳定的频率输出。该器件的主要特点如下:1)该合成器的输出频率为0.5~6 GHz;2)工作电压:2.7~3.3 V;3)最高鉴相输入104 MHz,具有4组可编程双模分频器8/9,16/19,32/33,64/65;4)编程控制采用3线串行接口;5)能够进行模拟和数字锁定检测;6)具有良好的相位噪声参数。

2.3 环路滤波器设计

在锁相环频率合成器中,环路滤波器的主要作用是滤除PLL输出误差电压中的高频分量以保证环路的稳定性,以改善环路跟踪性能和噪声性能。在环路带宽内,鉴相器强迫VCO跟踪参考频率,将参考振荡器的相位噪声映射到VCO上。这一过程受到鉴相器噪声基底的支配,因为鉴相器噪声基底通常比参考振荡器的相位噪声高。由于补偿频率高于环路带宽,环路就不能很好地跟踪参考频率,总的相位噪声等于VCO的相位噪声,因此要将环路带宽设置在鉴相器噪声基底与VCO自由振荡时相位噪声的交叉点上。过宽的环路带宽虽然能缩短锁定时间,但同时也会引入参考杂散;过窄则正好相反。因此需要在锁定时间和参考杂散之间作折衷考虑。通常环路滤波器的带宽应为鉴相器鉴相频率的1/10,同时为了避免环路不稳定,环路带宽不应超过鉴相频率的1/5。本设计中采用三阶无源积分滤波器,滤波器各参数由软件ADIsimPLL计算可得。PLL和环路滤波器如图3所示。

- 3D IC设计打了死结?电源完整性分析僵局怎么破(09-21)

- 快速调试嵌入式MCU设计仿真的三大因素浅析(12-12)

- 访问电源参考设计库的众多理由(12-09)

- 开关电源设计中如何选用三极管和MOS管(12-09)

- 一款常见的车载逆变器设计电路图(12-09)

- 电子工程师必备:电源设计及电源测评指南(12-09)