一种X波段频率合成器的设计方案

2.4 时序控制电路设计

本文利用FPGA对DDS芯片的串口控制寄存器直接进行送数操作以及对相关管脚的配置来实现对该DDS芯片的控制。

AD9910在串行通信模式下,对芯片管脚读写操作时序关系如图4所示,在片选信号CS低电平时开始对串口寄存器进行读写操作。指令周期中的8位数据的第一位为读写控制位,后7位表示为寄存器地址。数据周期紧接指令周期之后,送完数据后再将片选信号置位。注意输入的数据暂时存在寄存器的缓存器中,还需要IO_UPDATA(59脚)上升沿脉冲触发后才有效。同时,在设置IO_UPDATA时确保脉宽大于一个周期的内部信号SYNC_CLK。

3 性能分析

3.1 相位噪声

频率合成器的相位噪声主要由4部分组成:VCO固有的相位噪声;鉴相器、环路滤波器、分频器的相位噪声;参考频率的相位噪声以及VCO输出经二倍频后引起的相噪恶化值。其中环路分频比N对环路带宽内的输出相位噪声影响最大,即在环路带通内,输出相位噪声要恶化20logNdB。在环路带宽外的相位噪声主要由VCO,而VCO的相位噪声一般都比较理想,能满足工程需要。VCO输出经二倍频后引起的相噪恶化值为。在将VCO的特性理想化的情况下,则整个环路的相位噪声可近似为:

PNtot=PNPLL+201gN+10lgfPFD+20lg2 (5)

式(5)中PNPLL是锁相环的相位噪声基数,它是由锁相电路本身引起的,对于确定的锁相环和参考频率它是—常数,锁相芯片ADF4106的相位噪声基PNPLL为-219 dBc/Hz,式(5)中fPFD=fDDS/R,N=fVCO/fPFD=BP+A,因此(5)式可以写为:

PNtot=PNPLL+20lg(fVCO/fPFD)+10 lg(fDDS/R)+20 lg2 (6)

当频率合成器输出为中心频率9.4 GHz时,fVCO为4.7 GHz,通过改变频率控制字K使fDDS为47 MHz,取R=1,则频率合成器的相位噪声为:

PNtot=-219+201g100+10lg(47×106)+6=-219+40+77+6=-96 dBc/Hz (7)

图5为通过软件ADIsimPLL计算得到的相位噪声曲线。由该曲线可知,在偏离载频10 kHz时,相位噪声约为-95 dBc/Hz,在偏离载频1 MHz时,相位噪声约为-96 dBc/Hz,由此表明该频率合成器具有很好的相位噪声指标,可以满足设计要求。

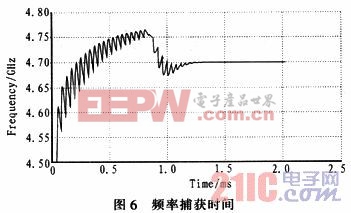

3.2 捕获时间

捕获时间是在一定的频率容限内由从一个特定频率跃变到另一特定频率所用的时间。跳变量通常由锁相环频段内的最大跳变决定。DDS激励PLL时,频率合成器的捕获时间主要由PLL的决定。当鉴相器工作在较高的频率上时,相位比较也将以较高的速度进行,从而锁相环将更快锁定。另外,由于锁相频率较高,环路带宽也将增大,这也会缩短捕获时间。当锁定频率为4.7 GHz时的捕获时间如图6所示。由图4知,经2 ms后PLL可将频率锁定在4.7 GHz上,由此表明该频率合成器具有较短的捕获时间。

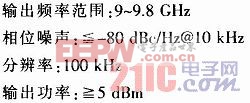

根据以上的设计方案,现已研制出样机。经Agilent公司的频谱仪E4407B测试,得知该频率合成器的性能参数主要有:

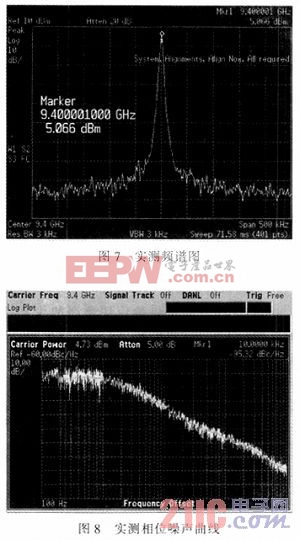

图7为频率合成器输出为9.4 GHz时的频谱,图8为其相位噪声曲线。

由图7可知,当输出为9.4 GHz时,实际输出频率与之相差1 kHz,表明该频率合成器输出精度高;由图8可知,当在偏离载频10 kHz处,相位噪声达-95.32 dBc/Hz,与理论分析基本吻合,从而证明该频率合成器设计是正确合理的。

5 结束语

本文采用ADI公司的AD9910和ADF4106设计了一个倍频式DDS激励PLL的X波段频率合成器,既利用了PLL的高鉴相频率以保证快的转换速度,又利用DDS保证高的频率分辨率,既解决高频率转换速度和高频率分辨率之间的矛盾,又保证了整个频率合成器的相位噪声。经测试表明,该频率合成器能产生低相噪、高分辨率、高稳定度的X波段信号,是一种较新的、实用的频率合成器,具有较好的工程应用价值。目前,该频率合成器已经成功的应用在某X波段非相参雷达测试设备中,并且可以很好的满足系统的要求。

- 3D IC设计打了死结?电源完整性分析僵局怎么破(09-21)

- 快速调试嵌入式MCU设计仿真的三大因素浅析(12-12)

- 访问电源参考设计库的众多理由(12-09)

- 开关电源设计中如何选用三极管和MOS管(12-09)

- 一款常见的车载逆变器设计电路图(12-09)

- 电子工程师必备:电源设计及电源测评指南(12-09)