技术讲座:用氧化镓能制造出比SiC性价比更高的功率元件(二)

基板成本也较低

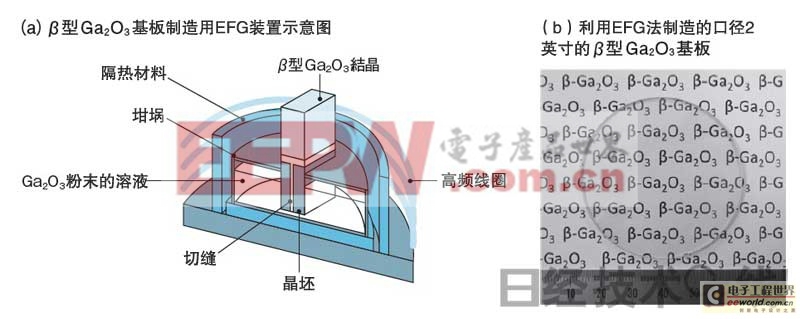

采用β-Ga2O3制作基板时,可使用“FZ(floating zone)法”及“EFG(edge-definedfilm-fed growth)法”等溶液生长法,这也是其特点之一(图4)。溶液生长法容易制备结晶缺陷少、口径大的单结晶,因此能够以低成本轻松量产基板。实际上是利用FZ法或EFG法制备单结晶,然后将结晶切成薄片,以此来制造基板。

图4:可利用溶液生长法

β-Ga2O3可利用FZ法及EFG法等溶液生长法(a)。已试制完成口径为2英寸的基板(b)。

用于制造蓝色LED芯片的蓝宝石基板就是利用EFG法制造的。蓝宝石基板不仅便宜而且结晶缺陷少,而且口径较大,达到6~8英寸。而SiC基板的基础即单结晶则需利用“升华法”制造,GaN基板的基础即单结晶需利用“HVPE(hydridevapor phase epitaxy)法”等气相法制造,因此在减少结晶缺陷和大口径化方面有很大难度。

日本信息通信研究机构等的研究小组试制出的晶体管所使用的β-Ga2O3基板是利用FZ法制成的。外形尺寸也很小,只有6mm×4mm。

但只要导入与蓝宝石基板相同的大型制造设备,就有望利用EFG法实现6英寸口径。估计将来能够以1万日元以下的成本实现1块口径6英寸的β-Ga2O3基板。

制造时的耗电量也很小

β-Ga2O3不仅可降低基板成本,而且还可降低制造时的耗电量及设备成本。比如,据计算,采用EFG法时,制造基板的单位面积耗电量只有升华法的约1/3。

制造时耗电量小的原因在于生长速度快,以及结晶生长时温度略低等。β-Ga2O3结晶的生长速度达到SiC的10倍以上。此外,升华法必须在2000℃以上的高温下使结晶生长,而且EFG法只需要1725℃。

不仅是基板制造,在基板上形成的处延层也能够以低于SiC及GaN的低温来形成。SiC及GaN的话一般要在1000℃以上的高温下使处延层生长。而β-Ga2O3基板在采用名为“mist CVD法”外延层生长方法时,生长温度可降至不到500℃。由于可降低基板制造和外延层生长时的温度,因此不仅是功率元件本身,连元件制造时的耗电量也可减少。

另外,由于不需要像SiC及GaN那样的耐热性高的制造设备,因此还有助于降低设备成本。

采用适合用来验证的简单构造

为了挖掘β-Ga2O3的这些出色潜能,我们开始对该材料进行研发。第一项成果就是上篇文章中提到的MESFET。尽管是未形成保护膜的非常简单的构造,但耐压却高达257V,且泄漏电流只有5μA/mm(图5)。

图5:使用β-Ga2O3试制晶体管

试制的β-Ga2O3的MESFET采用圆形电极图案(a)。虽然构造简单,但耐压却高达257V(b、c)

MESFET在多种FET中构造最简单、最容易制造,适合用来验证工作性能。

此次使用了通过掺杂Mg实施半绝缘化处理的单结晶β-Ga2O3基板。基板尺寸为6mm×4mm。晶面方向利用可将外延生长速度比其他面方向最大提10倍左右的(010)面。

在该基板上利用分子束外延(MBE)法形成作为沟道层的n型Ga2O3层。厚度为300nm,为制成n型掺杂了Sn。

进行二次离子质谱分析(SIMS)后表明,n型Ga2O3层的Sn浓度达到7×1017cm-3。

采用圆形电极

β-Ga2O3的绝缘技术还在开发之中,因此此次采用了圆形电极图案。采用该图案时,只会在内侧的源极及与外侧的漏极两电极间产生电场。这时,电流在两电极间完全断开,因此漏极电流不会泄漏到图案外部,无需绝缘。在源区、漏区及栅区的电极中,先形成了源区和漏区的欧姆电极。具体做法是:首先利用光刻技术形成图案;然后利用BCl3/Ar混合气体对相当于光刻后窗口部分的n型Ga2O3薄膜实施“反应性离子蚀刻(RIE)处理;最后,在RIE部分蒸镀Ti(20nm)/Au(230nm),并通过剥离它们来制作源极和漏极。

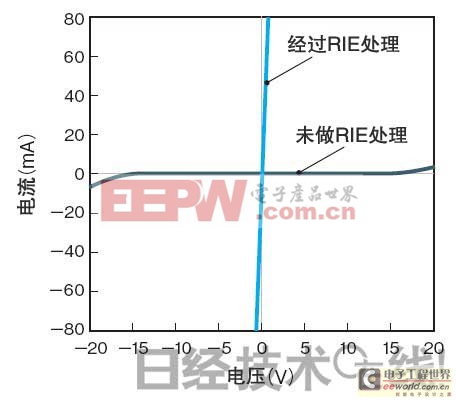

进行RIE处理后,源区与漏区的Ti/Au电极间的电阻值会大幅减小,电流可轻松流过。这是因为,RIE处理使电极间的接触从肖特基接触变为欧姆接触(图6)。

图6:通过RIE处理使电流轻松流过

通过实施RIE处理,可使电流轻松流过。原因是电极接触特性由肖特基接触变为欧姆接触,电极接触部的电阻值变小。

形成源极和漏极后,再次利用光刻技术形成图案,这次不进行RIE处理,而是直接在相当于窗口部分的n型Ga2O3薄膜上蒸镀Pt(15nm)/Ti(5 nm)/Au(250nm)。之后在进行剥离,制成肖特基结的栅极电极。此次试制品的目的只是为了验证工作情况,因此未在元件表面形成保护膜。试制品的栅极长度为4μm,源漏间距为20μm。漏极尺寸为直径200μm。另外,此次试制的晶体管在源极与漏极之间配置有测定时接触探针的栅极焊盘电极部分,因此无法明确定义栅极宽度。不过,以漏极的外周长度作为栅极宽度的话约为600μm。

实际耐压超过250V

试制品在施加+2V栅极电压时,最大漏极电流为16mA,漏

- 1200V CoolSiCTM MOSFET兼具高性能与高可靠性(06-28)

- 为ASIC和SoC选择最优嵌入式存储器IP(12-08)

- 美高森美发布创新SiC MOSFET系列(06-05)

- SiC元件“真命天子” 沟道MOSFET即将实用化(01-17)

- OTN帧头定位电路优化研究(12-26)

- 在光伏逆变器中运用SiC BJT实现更低的系统成本(11-29)