以较高的开关频率在负载点 (POL) 应用中工作

摘要: Power Clip 33 封装十分新颖,旨在增加同步整流 (SR) 降压应用中的功率密度,同时使用与传统分立式 Power 56 封装相比明显较小的 PCB 面积。 本文详细分析飞兆 Power Clip 3.3x3.3 Dual 是如何实现这一性能的。

概述

本文:

a. 总结了通过 Power Clip 封装实现的电源系统尺寸和电流密度的改进

b. 详细介绍了实现性能提升的 Power Clip 的特性

c. 提供了一对设计示例,展示通过该小占位面积和高频设计实现的总体元件占位面积减少

d. 展示了将 Power Clip 与传统设计在效率、功率损耗、波形、温度和热阻方面进行比较的测量数据。

简介

对电源工程师来说,功率密度 (A/mm2) 是器件选型中的一个重要指标。Power Clip Dual MOSFET 的设计是经过针对性的优化,可为同步降压调节器应用提供异常高的功率密度。

全新的 Power Clip 3.3x3.3 是对优化品质因数 (FOM)的硅技术和增强的散热设计的高效结合。

图1和图2展示这一新产品相较于两个竞争产品的性能。 新 Power Clip 较这两者性能都好。

图1显示,与较大尺寸的 5x6 竞争产品相比,Power Clip 的效率更高。 图1中的散热图片是在测试结束时拍摄的。 较小的 Power Clip 能够以同等的 TJ处理额外的 3 A 负载。

图2显示,与同等尺寸的 3.3x3.3 竞争产品相比,Power Clip 具有更好的效率和温度。 图2中的散热图片是在测试结束时拍摄的。 Power Clip 以低6 °C 的 TJ 温度处理了额外 8 A 的负载。

注意,这一图2评测使用与图1不同的控制器完成,因此 Power Clip 结果略有不同。

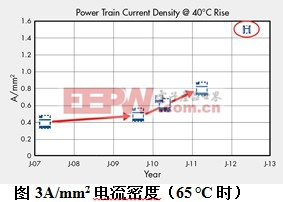

图3展示了过去 6 年中测试的一系列飞兆评测板的功率密度的演化。 Power Clip 产品实现的密度是上一代产品的近两倍。

这得益于 PowerTrench®工艺和封装技术的改进。图4展示了 Power Clip 33 MOSFET Asymmetrical Dual MOSFET 设计在负载点 (POL) 或同步整流 (SR) 降压转换器应用中的演化。 Power Clip 33 MOSFET 将一对分立式 MOSFET 的最佳的特性结合到 3.3x3.3 mm 的封装上。

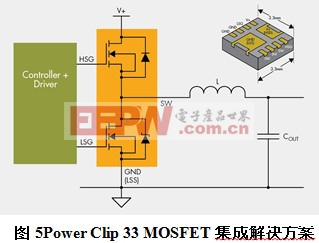

本文通过 Power Clip 33 MOSFET 展示了小尺寸元件解决方案的高频性能(参见图5),以及与传统分立式 Power 56 封装相比带来的效率提升。

Power Clip 33 MOSFET 封装

Power Clip 33 MOSFET 拥有卓越的高频开关操作性能。 关键设计特性是:先进的低 FOM 硅技术,结合一个散热优化的低电感铜夹互连封装。 它拥有最少的占位面积,使其更易于布线设计。

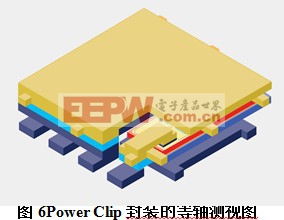

图6展示了封装结构的关键元素。 在这个双晶圆封装中,高侧 (HS) MOSFET 漏极朝下。 低侧 (LS) MOSFET 源极朝下。 从 HS 源极到 LS 漏极的互连通过一个大型铜夹完成。

如图7所示,相对于传统封装设计,比如分立式 Power 33、Power 56 或 Power Stage 56 Dual,寄生电阻和电感实现了大幅性能提升。

最大限度地减少电源路径寄生参数 – 要让一个同步降压电源拥有最优开关速度,必须最大限度地减少高频 (HF) 开关路径中的封装寄生电感;V+ 到 SW 到 GND (图5);并且必须最大限度地减少 V+ / GND 输入电容与 MOSFET 封装引脚之间的物理距离。 Power Clip 设计通过使用一个漏极朝下 HS MOSFET、晶圆之间的铜片夹和源极朝下 LS MOSFET 来实现这一点。 这实现了最小阻抗开关路径,其中在高频电源开关路径中无封装接线。 电源路径中唯一的互连是一个低电感、低电阻的铜夹。

增强的热性能 - 结构还优化了热性能。 典型 PCB 设计上的两个铺铜区域是 V+ 和 GND。 HS 漏极朝下 和 LS 源极朝下的 Power Clip 设计支持封装脚位与这两个铺铜区域之间的大面积连接。 铜夹支持卓越的晶圆与晶圆之间的热耦合。 这个独立于 HS 与 LS 晶圆之外的功率分区使两个晶圆之间具有低 RΘJA 热阻抗。

先进的硅技术 - 在该设计中使用的 MOSFET 技术是屏蔽栅极 PowerTrench® 工艺。 HS 和 LS 都设计有低单位面积电阻或 RSP,(m?/单位面积),以及低栅极电荷或 QGD,硅。 两个 MOSFET 都是极低 FOM (QGD*RSP) 元件。

图8展示了飞兆归一化 RSP和归一化 FOM (QGD*RSP) 的长期改进。 飞兆在这两个参数上都实现了一致的大幅改进。 传导损耗直接与 RDS(ON)成正比,而开关损耗直接与 QGD相关。 对于一个给定 RDS(ON) MOSFET,随着其 FOM (QGD*RSP) 的减少,QGD 和开关损耗也随之减少。 飞兆的设计改进同时降低了两个损耗系数。

通过减少 RSP,飞兆能够为典型的电源系统设计较小的晶圆。 晶圆尺寸越小,栅极电荷 (QG) 和 QGD也就越校 较小的晶圆尺寸也允许使用较小的封装,从而使封装寄生参数减少。 最终得到的是一个

- 用于低成本高效率离线LED驱动器的初级端调节技术(05-14)

- 通过初级端调节满足充电器能效规范(10-29)

- 大功率LED照明恒流驱动电源的设计(10-15)

- 利用低端栅极驱动器IC进行系统开发(12-21)

- 选择高压场效应管实现节能(06-13)

- 确定功率MOSFET的适用性(07-27)