素時才能複製它當成延伸;在右邊界時,想要取得已經掃瞄過的像素當成延伸則需要利用到暫存器。

我們可以發現,必須要等到掃描第二列第二行時,邊界處理器才會有第一次的輸出(DIN_1、DIN_2與DIN_3是同時輸出的)。因此,可設計出如圖4.3之架構。

4.1.3 兩種情況同時發生

當兩種情況同時發生時,延伸之方法如圖2.6所表示。

4.2 記憶體

從圖3.6的儲存方式來看,雖然掃描時一次是一個像素值,不過利用暫存器並且合成,儲存時便可一次存兩個像素值,並且可以在輸入前取DEven為YU;Dodd為YV。而輸出時也可利用暫存器並且做分解,如圖4.4所示。

在控制讀寫方面,需要注意的是當掃描到偶數列時,儲存奇數列之記憶體的讀寫腳位會一直維持在讀的狀態;而掃瞄到奇數列時,儲存偶數列之記憶體的讀寫腳位也會一直維持在讀的狀態。

4.3 計算處理器

依照圖2.4做拆解運算,如圖4.5(a)(b)(c),可以看出只需要兩個1x3的濾波器和一些暫存器就可以完成圖2.4的拆解動作。

因此計算處理器的設計上最為簡單,其中大部分是由組合電路所組成。如圖4.6所示。

其中的暫存器R1與R2是為了將ALU_1所計算出的結果暫存起來,如圖4.7。ALU_1及ALU_2的作用是為了做加權函數的計算,輸出為 DIN_1 + 2*DIN_2 + DIN_3 ,但須注意的是ALU_1輸出及ALU_2輸入位元大小的設定,以免發生溢位。最後再將ALU_2的輸出向右位移4位元(函數計算中的除以16),DOUT即為做完加權計算的Y值。

第五章 設計與驗證之流程

在本章節中,我們將簡單的介紹LPF設計流程,接著,會利用一組的測試資料,來驗證模擬結果是否正確。

5.1 設計流程

如圖5.1所示,一開始先考慮架構之功能,接著使用硬體描述語言Verilog HDL 實現功能之設計,經過編譯器確定語法無誤後,再模擬結果。若有問題,則回頭尋找錯誤;若沒有問題,則完成全部設計之流程。5.2 模擬及驗證

完成RTL之後,接著要模擬及驗證結果是否正確。首先要先將.ppm檔轉換成.dat檔,因為這是Verilog HDL中testbench所能夠讀取的檔案。我們除了用Verilog HDL來模擬421低通濾波器之外,也使用C語言模擬421低通濾波器,並將兩者輸出之結果儲存成.dat檔來比較。若結果無誤,則轉換回.ppm檔。

5.3 波型圖

當模擬完成之後,使用Verdi觀察波型圖。

5.3.1 低通濾波器

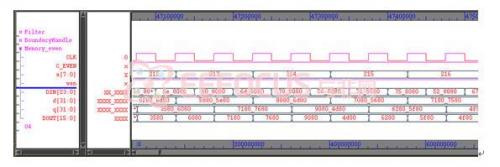

圖5.3(a)(b)說明了當讀取資料為圖片的開頭之前或結尾之後時,VS會為1;否則為0。當讀取資料為圖片每行的開頭之前或結尾之後時,HS會為1;否則為0。

5.3.2 邊界處理器

在之前提到邊界處理器需要利用到暫存器並位移。如圖5.4所表示,R1、R4、R7、R10分別為DIN_1延遲一個、兩個、三個及四個時脈週期;R2、R5、R8、R11分別為DIN_2延遲一個、兩個、三個及四個時脈週期;而R3、R6、R9、R12分別為DIN_3延遲一個、兩個、三個及四個時脈週期。

圖5.4 邊界處理器

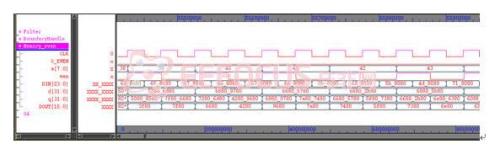

5.3.3 記憶體

記憶體在控制讀寫方面,需要注意的是當掃描到偶數列時,儲存奇數列之記憶體的讀寫腳位會一直維持在讀的狀態;而掃瞄到奇數列時,儲存偶數列之記憶體的讀寫腳位也會一直維持在讀的狀態。圖5.5(a)是掃描到奇數列時,而圖5.5(b)則是為掃描到偶數列時。可注意到WEn的差異性。

圖5.5(a) 儲存偶數列之記憶體

圖5.5(b) 儲存偶數列之記憶體

5.3.4 計算處理器

可以看出利用暫存器的位移便只需要兩個1x3的濾波器即可達到原本要求之函數加權計算。

圖5.6 計算處理器

|