基于网络编码的多信源组播通信系统,包括源代码,原理图等(四)

4结论

网络编码从提出到现在已有十年,在这期间,网络编码的理论研究和工程应用不断发展和成熟,基于网络编码的多信源组播系统是网络编码在硬件方面的实现。它突破了以往网络编码的应用研究只停留在软件和虚拟网络,通过搭建实际的组播通信网络,并应用NetFPGA平台使网络编码在硬件中得以实现。

文档的前面分别介绍了网络编码的基本概念和研究动态、编解码策略和算法以及编码、转发、解码三个系统的详细设计方案,包括系统的软硬接口和软件的基本功能。由于系统中的网络编解码都是由硬件完成,软件的功能主要是控制和测试时使用,因此方案设计以硬件为主。

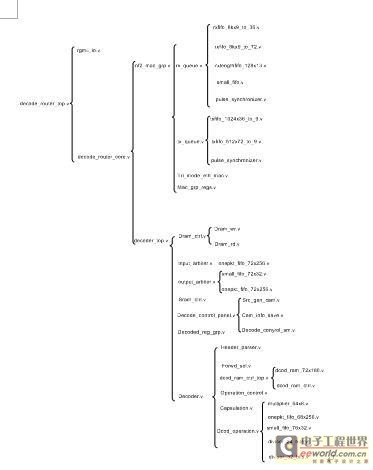

图4-1,图4-2和图4-3分别是编码、转发以及解码路由器三个系统的verilog代码树状图,除去MAC层和core generator产生的代码,代码量有11,000行。附录给出了编码路由器和解码路由器中的关键代码。

图4-1 编码路由器代码树状图

图4-2 转发路由器代码树状图

图4-3 解码路由器代码树状图

附录

附1:编码路由器核心代码:编码模块: payload_router.v

/////////////////////////////////////////////////////////////////////////////

// vim:set shiftwidth=3 softtabstop=3 expandtab:

// Copyright(c) 2009, All rights reserved.

// Advanced Network technology Lab, Shenzhen graduated school of PKU

// Module: payload_router.v

// Project: nf2_coding.ise

// Time and Author: 2009-12-25 liyining

// Description:determine whether should carry out coding operation, and route

// the packets

/////////////////////////////////////////////////////////////////////////////

`define DLY 1

`timescale 1ns/1ns

module payload_router

#(parameter DATAWIDTH = 64,

parameter CTRLWIDTH = DATAWIDTH / 8 //bit-width parameter

)

(

//payload fifo 1 port

input [DATAWIDTH - 1:0] data_payloadfifo_router_1,

input [CTRLWIDTH - 1:0] ctrl_payloadfifo_router_1,

input empty_payloadfifo_router_1,

output reg rd_en_payloadfifo_router_1,

//payload fifo 2 port

input [DATAWIDTH - 1:0] data_payloadfifo_router_2,

input [CTRLWIDTH - 1:0] ctrl_payloadfifo_router_2,

input empty_payloadfifo_router_2,

output reg rd_en_payloadfifo_router_2,

//multiplier 1 port

input rdy_router_multiplier_1,

output reg [DATAWIDTH - 1:0] data_router_multiplier_1,

output reg first_dword_1, //flag to indicate the start of a pkt. only when it is the first double word of a pkt, should the random number be updated.

output reg val_router_multiplier_1,

//multiplier 2 port

input rdy_router_multiplier_2,

output reg [DATAWIDTH - 1:0] data_router_multiplier_2,

output reg first_dword_2, //flag to indicate the start of a pkt. only when it is the first double word of a pkt, should the random number be updated.

output reg val_router_multiplier_2,

//rand number generator port

output reg rand_num_en, //enable the random number generator

input rand_num_val,

//packing fifo port

input rdy_router_packingfifo,

input empty_packingfifo, // only when the whole last pkt is sent out, and the packing fifo is empty, then proceed the next pkt

output reg [DATAWIDTH + CTRLWIDTH:0] data_router_packingfifo, //an extra bit(MSB) to indicate whether it is a coded pkt

output reg val_router_packingfifo,

output reg [2:0] router_status, //send router_status to packing_fifo, indicate where to get data

//misc

input clk,

input rst_n

);

reg [DATAWIDTH - 1:0] data_temp1;

reg [CTRLWIDTH - 1:0] ctrl_temp1;

reg [DATAWIDTH - 1:0] data_temp2;

reg [CTRLWIDTH - 1:0] ctrl_temp2;

reg [1:0] counter_getdata; //counter for the read-FIFO-delay, 1 clock circle

parameter JUDGE = 3'b000;

parameter GET_DATA2 = 3'b001;

parameter SEND_DATA2 = 3'b010;

parameter GET_DATA1 = 3'b011;

parameter SEND_DATA1 = 3'b100;

parameter GET_BOTH = 3b101;

parameter GET_BOTH = 3'b101;

parameter SEND_BOTH_1 = 3'b110;

parameter SEND_BOTH_2 = 3'b111;

always @(po

源代码原理 相关文章:

- 基于网络编码的多信源组播通信系统,包括源代码,原理图等(二)(12-06)

- 基于网络编码的多信源组播通信系统,包括源代码,原理图等(一)(12-06)

- 电源设计小贴士 1:为您的电源选择正确的工作频率(12-25)

- 用于电压或电流调节的新调节器架构(07-19)

- 超低静态电流电源管理IC延长便携应用工作时间(04-14)

- 电源设计小贴士 2:驾驭噪声电源(01-01)