基于网络编码的多信源组播通信系统,包括源代码,原理图等(二)

2 多信源组播系统结构及整体设计方案

2.1项目研究需求、目标和内容

网络编码能够提高网络吞吐量,提升鲁棒性、安全性等网络性能。具有网络编码功能的路由器是未来网络发展的趋势。组播通信在网络通信中有重要的作用,事实上,任何一个网络都可以认为是组播网的一个特例。然而,目前在世界上研究网络编码在组播上的应用大多集中在单信源组播方面,例如,单信源多信宿网络如何达到最大传输速率问题[25],基于网络编码的组播路由算法和性能评估[26], 基于网络编码的组播通信网络的拓扑设计[27], 多信源随机线性网络编码在组播通信的研究[28]以及单信源组播网中编码节点的研究[29],以上研究都是以软件仿真为主,没有形成实际的硬件平台和系统。

多信源组播的应用非常广泛,如P2P内容分发网络等。事实上,任何一个网络都可以作为多信源组播的一个特例,因此研究多信源组播是有意义且必要的。

本项目的主要研究目标是基于网络编码的多信源组播系统的实现。在基于国内外网络编码理论在组播通信中的最新研究成果和技术,对网络编码理论进行深入学习和探讨,提出一种基于网络编码的多信源组播系统和网络,然后依据此系统设计出可实现组播的通信协议和相关算法,再利用开放式的网络设计硬件平台NetFPGA[30],使提出的协议和算法在硬件上实现,最后在实际的环境中用若干电脑和NetFPGA组成一个小型组播通信网络进行系统测试和性能评估。

2.2 NetFPGA——新一代开放式网络研究平台简介

由斯坦福大学开发的NetFPGA是一个基于Linux操作系统的可重用开放性硬件平台,允许用户在实验室内搭建高性能的网络模型进行仿真和研究。它具有以下特点[31]:

(1)很好地支持模块化设计,它可以使研究人员在硬件上搭建Gb/s高性能网络系统模型。(2)NetFPGA是一个基于Linux系统的开放性平台,可以利用平台上现有的资源,在前人开发的基础上添加自己的模块和修改现有的系统,而不需要重复地搭建外围模块、开发驱动和GUI等,大大减轻了网络研究的任务。

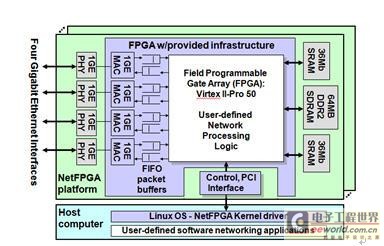

NetFPGA的硬件主要包含了4个1Gb/s的以太网接口(GigE),一个用户可编程的FPGA,以及两片SRAM和一片DRAM。NetFPGA开发板通过标准的PCI总线接口连接到PC机或服务器,模块框图如图2.2-1所示。

图 2.2-1:NetFPGA平台的组成框图

在外部硬件接口方面,除了连接PC主机的PCI总线插口,一个Broadcom公司的物理层收发器(PHY)包含了四个千兆位以太网接口,板子上的两个SATA连接口使得系统内部的多个NetFPGA可以通过SATA数据线连接起来,互相之间直接以很高的速度交换数据,而不必再通过PCI总线。NetFPGA通过PCI总线与主机CPU连接,提供了硬件加速的数据通道,分担CPU的处理任务。主机CPU按照DMA方式读写NetFPGA上的寄存器和存储器来配置NetFPGA的工作模式,并对NetFPGA的工作状态进行监控。

NetFPGA平台的软件系统包括操作系统、作为软件接口的驱动程序、实现各种硬件功能的逻辑代码、执行控制功能的软件程序、系统测试的脚本程序,以及计算机辅助设计软件工具。

2.3 利用NetFPGA实现本设计的总体构想

基于网络编码的组播通信系统将充分运用NetFPGA上面的各种硬件和软件资源,实现系统的设计目标,具体是:(1)根据项目的需求,合理且充分利用NetFPGA卡上面的各种硬件资源,如FPGA、存储芯片和输入输出接口;(2)由于基于NetFPGA实现的IPv4原理性路由器是一个开源的系统,因此我们可以运用其提供的部分代码和已经设计好的底层硬件平台,来帮助我们实现设计目标。例如,我们的系统的编码、解码工作主要在网络层完成,因此我们可以利用NetFPGA中已有的物理层、MAC层硬件逻辑来实现数据的接收和发送;(3)在软件方面,由于NetFPGA平台选择了CentOS操作系统,并且开发了软硬件接口的驱动程序,基于Linux内核的设备驱动程序和Java程序开发的图形用户界面(Java GUI)等,因此我们可以对其应用、改进,使我们的系统更加完善,方便调试和后续的进一步研究。

2.4系统实现的整体设计方案说明

2.4.1 系统拓扑图及说明

如图2.4-1所示,是拟采用的组播通信网络的拓扑图:

图2.4-1基于网络编码组播的网络拓扑图

说明:为了易于在工程上实现,将网络编码路由器分为编码路由器EC(Encoding router)和解码路由器DC(Decoding router),分别专门负责编码和解码。具体讲,如图1所示,信源S1,S2,S3发送数据包,编码路由器EC0和EC1负责将接收到的数据包以随机的系数进行线性编码后发送给组播路由器R,注意,这里的组播路由器更准确地说是转发路由器,因为它的功能只是将收到的数据包转发到其三个输出端口

网络编码源代码原理 相关文章:

- 基于网络编码的多信源组播通信系统,包括源代码,原理图等(一)(12-06)

- 电源设计小贴士 1:为您的电源选择正确的工作频率(12-25)

- 用于电压或电流调节的新调节器架构(07-19)

- 超低静态电流电源管理IC延长便携应用工作时间(04-14)

- 电源设计小贴士 2:驾驭噪声电源(01-01)

- 负载点降压稳压器及其稳定性检查方法(07-19)