基于网络编码的多信源组播通信系统,包括源代码,原理图等(二)

读写策略

我们将解码后的数据包暂存在SRAM中等待发送,每个信源对应一个SRAM区域,同一个信源的解码后的人数据包存储在同一个RAM中,存储地址为该包的代的编号。每个RAM各有一个读指针,写数据按照RAM的地址大小顺序写入。读数据时按照信源编号和代的大小读取。由于发送速率一般会高于解码速率,因此RAM不用很大,暂定为256×1800。

每读取一个数据后,指针加1,若读取某个SRAM时无数据(可能是延迟或丢失造成),则不用等待,直接进行下一个SRAM的读取,3次轮询之后还没有到达,则强行加读指针加1,读取下一个数据包。如图2.4-11所示为SRAM的读写操作。

图2.4-11 二级缓存SRAM的读写操作

(6)举例说明

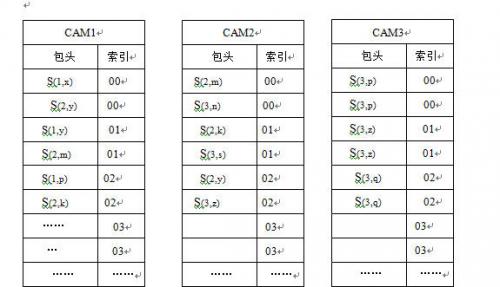

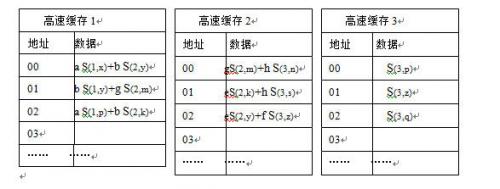

为了更清楚地显示整个解码的操作过程,我们以DC3为例,图2.4-12显示的是DC3的3个高速缓存和CAM,解码过程如下

图2.4-12 数据包S(1,x)解码过程

数据包S(1,x)解码过程如下:

先将S(1,x)的包头3个CAM中搜索,在CAM1中得到索引为00,我们利用该索引得到S(1,x)在高速缓存1的地址为00,从高速缓存1读取数据,得到a S(1,x)+b S(2,y),为了求解S(1,x)我们调用解码子任务先求解S(2,y),为了防止出现死循环,解码子任务只在CAM2和CAM3中搜寻S(2,y),在CAM2中得到地址为02,于是读取高速缓存2的02地址数据,得到eS(2,y)+f S(3,z),于是再调用子任务求解S(3,z),在CAM3中搜索S(3,z)后解出S(3,z), 于是可以解出S(2,y),最后再解出S(1,x),同时,分别将S(3,z)、 S(2,y) 、S(1,x)存入SRAM3,SRAM2,SRAM1相应的地址中。

2.5 系统软硬件接口及相关软件功能

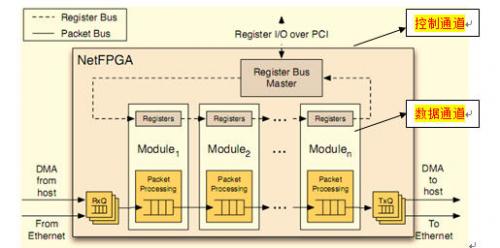

在系统中,并非只有硬件逻辑在不同的模块之间处理数据包,而且还有相应的软件和控制程序。如图2.5-1所示,是数据包在系统中的通道与处理流程。数据在系统中的通道分为data bus和register bus,data bus主要进行数据的硬件处理,register bus则是软硬件的接口。在数据传输的每个阶段对软件应该是可控的、透明的,这些软件在更高层次上执行更复杂的算法和协议,或者处理一些异常情况,同时,对于系统开发人员,也应该是可控的,因为开发人员往往需要配置和调试硬件。使用通用的寄存器接口就可以使数据处理对软件透明化,这是靠映射内部的硬件寄存器来完成的,即所谓的存储映射技术。对于软件来讲,映射寄存器相当于一个I/O接口,它可以由软件访问和修改。

图2.5-1:系统中的register bus 和data bus

Register bus中每个模块的register连接在一起,组成一个信息环路。这些register块中存储了数据处理在每个

模块中的状态和阶段,任何一个模块都可以响应来自PCI总线寄存器的访问和控制要求,而PCI总线寄存器可以通过软件来控制。也就是说,硬件和软件的通信是通过PCI总线完成的。

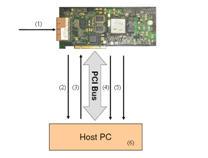

数据以及控信息在硬件和主机系统之间是通过PCI总线传输的,以Linux网络存储栈作为接口的。NetFPGA向主机发送分组数据的过程如图2.5-2a所示:

分组到达,发往CPU队列;

中断程序通知驱动程序有分组到达;

驱动程序设置和初始化DMA传送器;

NetFPGA通过DMA总线发送分组;

中断程序发送DMA结束信号;

驱动程序把分组传递到网络存储栈;

图2.5-2a:NetFPGA向主机发送数据 图2.5-2b:主机向NetFPGA发送数据

主机向NetFPGA发送分组数据的过程如图2.5-2b所示:

控制软件通过网络socket发送分组,分组被递交给驱动程序;

驱动程序设置和初始化DMA传送器;

中断程序发送DMA结束信号;

主机访问寄存器是通过系统调用系统内核的ioctl( )函数作为接口的。读写寄存器的操作函数如下,这两个函数内部调用了ioctl( )函数。

readReg(nf2device *dev, int address, unsigned *rd_data)

writeReg(nf2device *dev, int address, unsigned *wr_data)

例如: readReg(&nf2, OQ_NUM_PKTS_STORED_0, &val);

主机访问NetFPGA寄存器的过程如下:

(1)控制软件调用ioctl( )函数操作网络socket,由函数ioctl传递给驱动程序;

(2)驱动程序完成PCI寄存器的读写

网络编码源代码原理 相关文章:

- 基于网络编码的多信源组播通信系统,包括源代码,原理图等(一)(12-06)

- 电源设计小贴士 1:为您的电源选择正确的工作频率(12-25)

- 用于电压或电流调节的新调节器架构(07-19)

- 超低静态电流电源管理IC延长便携应用工作时间(04-14)

- 电源设计小贴士 2:驾驭噪声电源(01-01)

- 负载点降压稳压器及其稳定性检查方法(07-19)