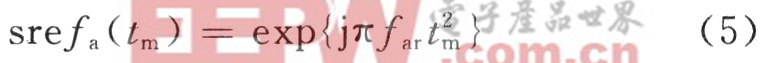

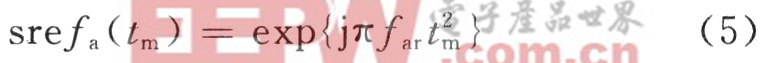

式中:far为多普勒调频斜率。

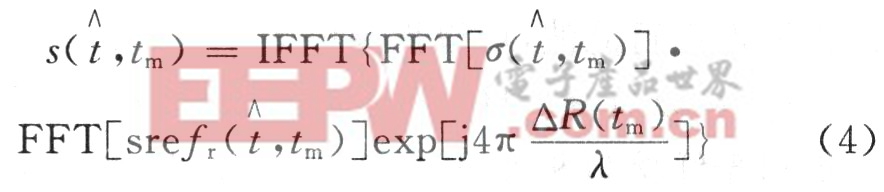

由于有斜视角引起多普勒中心不为零,对方位时域数据作相位补偿,补偿的相位函数是:

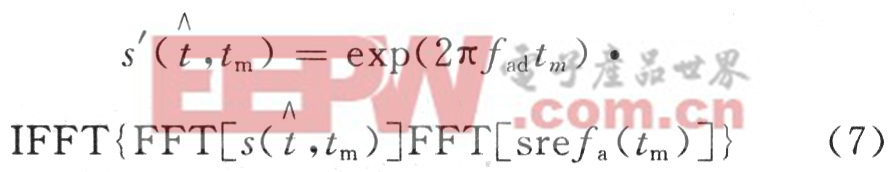

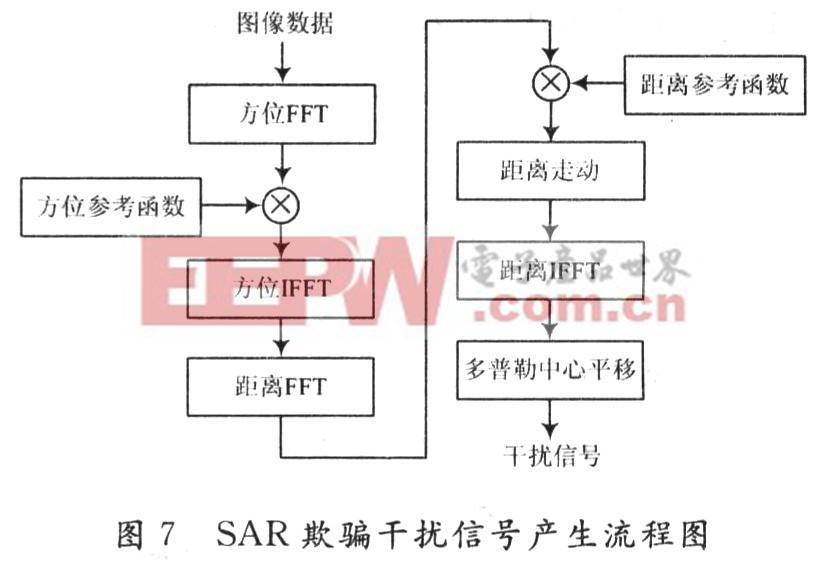

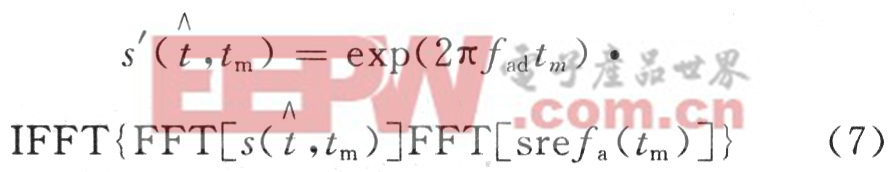

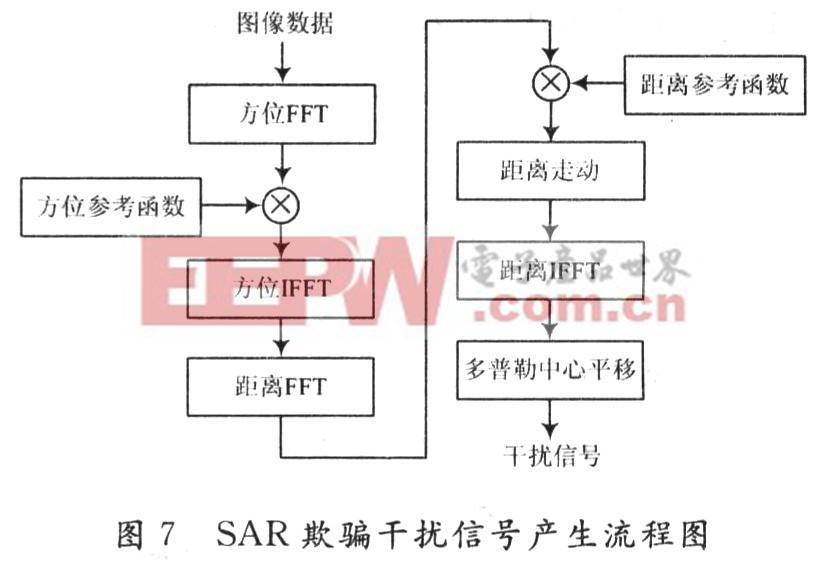

方位向欺骗干扰的实现是对方位向信号进行卷积处理,即:

经过二维卷积处理之后,可获得对应场景的干扰信号s′(t,tm)。

4 硬件设计注意事项

整个DRFM模块工作的频率很高,设计时应该严格按照高速电路的设计原则处理每一个细节。

4.1 时钟的设计

时钟电路设计的好坏直接影响高速电路的工作性能。为了防止高速时钟受到外界干扰或向外辐射干扰,需要把时钟的电源和地与其他的电源、地分开。差分信号可以有效的防止干扰,把送入的时钟转换为差分的LVDS或ECL等电平后再使用,可以有效提高时钟质量。板上送到不同地方而又有相位要求的两个时钟,例如送到两路ADC的时钟,走线要等长,并控制好阻抗。

4.2 电源和地的噪声

在高速电路中30%以上的噪声来自电源和地。对于一个印制板,电源、地和过孔构成了整个电源分布系统。板上的大量器件同时开关时需要较大的瞬时电流,这将会带来电源和地的波动,从而引入干扰。去耦是解决电源地噪声的有效方法,把合适的电容放置在器件的管腿附近进行滤波,可以提高电源稳定性。如果板上空间允许,可以放置尽量多的电容。该系统中的高速数据采集和光纤接口板采用光纤传输方式,光纤传输速率高,对电源比较敏感,需单独用稳压块提供供电,和其他3.3 V电分开。

4.3 信号的走线

关键信号尽量走在顶层或底层,这样容易控制阻抗并且可以避免过孔影响信号完整性。需要时用地线包住信号线,屏蔽干扰。过孔之间避免太近,容易引起互扰。尽量使同一层面信号线网的参考层面为地层,切勿以主要层面为电源层。 5 结 语

主要介绍了DRFM的硬件实现。其高速数据采集和宽带波形产生保证了系统的大瞬时带宽,6块并行DSP处理板使得系统具有极强的信息处理能力,便于相干干扰、噪声压制干扰等不同干扰样式的产生。大的存储容量使得系统可以保存脉宽很宽的样本信息。鉴于该DRFM由三部分组成,体积较大,数据中间传输过程较多。以后设计应该考虑模块化,小型化,方便调试。该设计已成功运用在某型号产品上,事实证明了其可靠性和稳定性。

|