一种数字射频存储器的设计

引 言

现代电子战孕育了DRFM的诞生,数字射频存储器是一种对射频信号采样、存储、运算然后转发的电子部件。DRFM对样本信息保存下来后,根据需要加入调制信息;再通过高速DAC转发出去,实现对目标的有效干扰。随着大规模集成电路、微波集成电路的高速发展,数据采集和波形产生的工作带宽已越来越宽,信号处理的速度也越来越快,这些都使得DRFM的成本大幅降低,而处理能力大大提高,从而得到了更为广泛的应用。

1 基本原理

接收系统将天线下来的射频信号经过放大、滤波、下变频为中频信号,高速数据采集在基带或中频完成模拟信号的数字量化,数据采集的采样率决定着DRFM的接收带宽。数字样本信号被存储在存储器中,在需要时可随时读取出来并加适当的处理,然后由高速数/模转换器转换为模拟信号,再经激励上变频变频到所需频段,释放有效干扰,其基本组成框图如图1所示。

2 硬件设计

考虑到所需设计的DRFM带宽宽,存储容量大,信号处理运算量大,整个DRFM分为高速数据采集、信号处理单元、干扰波形(高速D/A)3部分,且来分开设计。数据采集和信号处理单元的数据传输采用光纤传输方式,信号处理单元和干扰波形之间的通信采用TS101的LINK口传输方式。

2.1 高速数据采集的设计

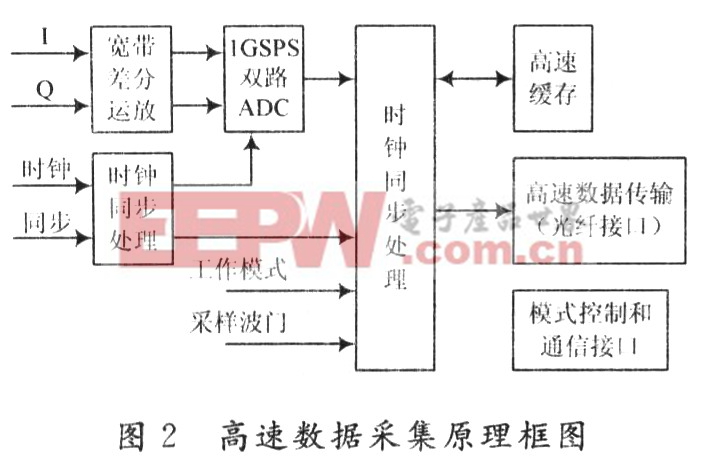

高速数据采集完成对正交的基带I,Q基带信号进行模/数转换、存储,再以光纤传输方式将样本信息送给后续信号处理单元。模/数转换芯片是数据采集的核心器件,这里采用Atmel公司的ADC芯片AT84AD001,其为采样率1 GHz、分辨率为8 b的双路ADC,输入电平峰峰值500 mV,16路LVDS电平输出和FPGA接口。FPGA采用Altera公司的EP2S90F1020。它集成了数百对差分管脚和大量的普通I,Q脚,方便与ADC和片外SRAM接口。其片内丰富的PLL资源使得时钟的产生变得更加容易。片外大容量的片外存储器(GS864436)保证了样本的海量存储。GS864436是总线速度高达200 MHz的SRAM,每片容量为2 M×32 b。由于ADC的采样率为1 GHz,就单路I来降数据率为1 GHz×8 b,如此高的数据率显然难以直接和SRAM接口。数据将在FPGA被降速为125 MHz ×64 b后再送到SRAM中。因此实际应用中2片存储器拼接为64 b后用来存储I路数据,2片存储Q路数据。和信号处理单元接口的光纤采用Agilent公司的2.5Gb/s光模块。该光模块为双向光纤,一个通道发送数据,一个通道接收。其原理框图如图2所示。

2.2 信号处理单元设计

干扰算法的复杂性决定了信号处理总的运算量是巨大的。目前极少有独立的运算处理单元能够满足系统处理能力的要求,因此如何构建一个并行处理系统是解决大运算能力的一个必要需求,在并行处理技术中如何协调组织各个处理单元并行工作是设计的一个难点所在。

信号处理单元包括6块TS板、1块光纤接口板、1块CPU板以及2块CPCI底板组成。光纤接口板负责接收数据采集送来的样本信号,再经过机箱的总线传把数据传输给各块DSP板,DSP板对样本作相关处理后,通过LINK口方式把产生的干扰信号送到D/A板。

作为信号处理单元的核心部件DSP板,其选择应满足实时性,大存储,高数据带宽的基本要求,同时应具备易于多板卡互连的接口。因此考虑以TS101为DSP运算单元的通用信号处理板,该板卡主要性能如下:

(1)单板处理能力。由4片内核时钟为300 MHz的TigerSHARC-TS101组成,总处理能力可提供7.2 GFLOPs浮点处理能力;外总线时钟为75 MHz。

(2)系统接口及数据带宽。4片TS101之间紧耦合互连,构成一个处理簇,簇内总带宽2 GB/s;DSP簇对外提供8个Link用于板间互连,每通道125 MB/s,板间总带宽1 GB/s;CPCI标准总线,33/66 MHz、32/64 b PCI接口;支持2个ePMC背板,提供33/66 MHz,32/64 b PMC接口;32 b自定义总线,可以为后插板提供数据传输;定时同步总线,可以保证处理机内所有板卡的硬件同步和时钟同步。

(3)存储容量。每个TS101片内带有6 MbSRAM,4片TSl01共享SDRAM最高2 GB,另外有2~4 MB ZBTSRAM内存。信号处理单元系统结构如图3所示。

图4为频偏100MHz信号经过接收机变频、基带解调为I,Q信号,再经过数据采集量化、存储、光纤传输后。在光纤接口板上所测的各项性能指标。图中可以看到:A/D的SNR为37.2 dB,镜像抑制度为33.55 dB,A/D有效位数达6.12 b。上述指标证明了接收机及高速数据采集设计的正确性。

2.3 干扰波形(高速DAC)设计

干扰波形通过LINK口接收信号处理DSP板卡发送过来的基带I,Q数据.并用片外SRAM对数

3 SAR干扰信号的产生

鉴于该项目的主要试验对象为机载SAR,就SAR干扰信号的产生过程作简单介绍。SAR回波的数学模型如下:

式中:σ(r,x)为目标二维反射特性;Wr(r)为SAR发射信号距离向天线方向图;h1(r,x)为方位响应函数,其为距离r和方位x的二维函数;h2(r,x)为距离响应函数,其为距离r的一维函数,与方位x无关。

可见,SAR回波信号可表示为目标散射特性σ(r,x)乘以距离向天线方向图Wr(r);再相继与两个脉冲响应函数h1(r,x)和h2(r,x)的卷积。这就是SAR模拟回波产生的二维卷积算法。二维卷积算法可用于欺骗干扰信号的产生,这时还需要根据SAR平台运动参数、平台与干扰站的相对位置进行必要的多普勒补偿。

二维卷积法具体实现算法如下:

假设干扰信号是场景分布函数σ(t,tm),其中t是距离向快时间;tm是方位向慢时间。距离走动量△R(tm)为:

- 直接变频接收机设计可实现多标准/多频带运行(10-11)

- 基于蓝牙芯片的无线通信模块设计与开发(02-03)

- 无线通信网络设计与现场测试(10-10)

- WiMAX数据传输加密方案设计与实现(05-25)

- 高性能TD-SCDMA接收机的设计(03-15)

- 初步设计WiMAX射频系统(03-29)