300Ω反馈电阻水平线与互阻幅度曲线的交叉点是环路增益为0dB的地方。在这个频率点,T(s)的相位接近-135°,因此有45°的相位余量。相位余量和稳定性随RF的增加而增加,随RF的减小而减校电流反馈放大器应始终使用具有足够相位余量的纯电阻反溃

PCB版图

在稳定的ADC驱动器设计好后,还必须在PCB上实现。由于电路板存在寄生成分,总是会损失一些相位余量,因此电路板的寄生效应必须保持最小,其中特别要关注的是负载电容、反馈环路电感和求和节点电容。每种寄生电抗都会给反馈环路增加迟滞性相位偏移,从而减小相位余量。由于PCB版图设计不良可能导致20°以上的相位余量损失。

在使用电压反馈放大器时最好使用尽可能小的RF,以便最小化由RF和求和节点电容组成的极点引起的相位偏移。如果要求使用大的RF,寄生电容可以用跨接每个反馈电阻的小电容Cf进行补偿,对Cf的要求是RFCf等于RG乘以求和节点电容。

PCB版图是设计中最后的必要步骤之一。遗憾的是,它也是设计中最容易被忽视的步骤之一,即使性能高度依赖于版图设计的高速电路也是如此。马虎或拙劣的版图设计可能降低一个高性能设计的性能,甚至使它不能工作。虽然本文无法涵盖正确高速PCB设计的所有方面,但还是要介绍一些关键点。

寄生成分将损害高速电路的性能。寄生电容是由元器件的焊盘、走线、地平面或电源平面引起的。没有地平面的长走线将形成寄生电感,进而导致瞬态响应中的振铃和其它不稳定现象。寄生电容在放大器的求和节点处特别危险,因为它会在反馈响应中引入一个极点,造成尖峰和不稳定。一种解决方案是确保ADC驱动器安装和反馈元件焊盘下方区域的所有电路板层都是干净的地和电源平面。

要使有害寄生电抗最小,首先要使所有走线尽可能短。RF-4印制板的外层50Ω走线产生的寄生参数大约为2.8pF/英寸和7nH/英寸。内层50Ω走线的寄生电抗将在此基础上增加约30%。还要确保在长走线下方有地平面,以使走线电感最小。保持短小的走线有助于减小寄生电容和寄生电感——并保持设计的完整性。

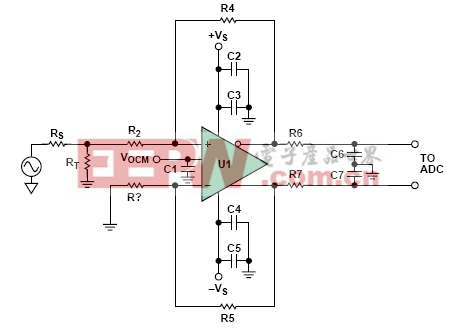

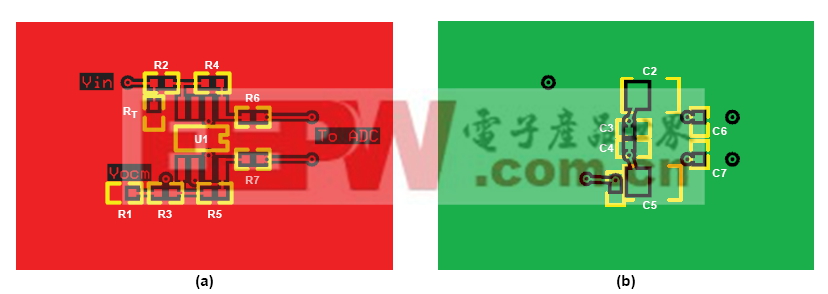

电源旁路是版图设计中另一个重要的考虑因素。确保电源旁路电容和VOCM旁路电容尽可能靠近放大器引脚放置。另外,在电源上使用多个旁路电容有助于确保为宽带噪声提供低阻抗路径。图21给出了一个带旁路和输出低通滤波器的典型差分放大器原理图。低通滤波器用于限制进入ADC的带宽和噪声。理想情况下,电源旁路电容回路靠近负载回路,这有助于减小地平面中的环流,从而改善ADC驱动器性能(图22a和图22b)。

图21:带电源旁路电路和输出低通滤波器的ADC驱动器。

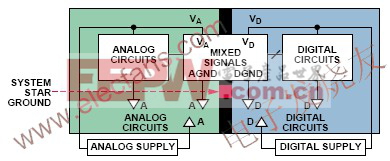

使用地平面和一般的接地技巧是一个具体而复杂的课题,不在本文讨论的范围之内。不过有几个要点需要指出,见图22a和图22b。首先,只在一个点将模拟和数字地连接在一起,记住只是单点接地。这样做可以使地平面中模拟和数字电流的交互作用最小,而这种交互最终将导致系统中产生“噪声”。另外,要将模拟电源终接到模拟电源平面,数字电源终接到数字电源平面。对于混合信号IC,要将模拟回路终接到模拟地平面,将数字地回路终接到数字地平面。

图22(a):器件侧。(b):电路侧。

图23:混合信号的接地方式。

我们希望当您用ADC驱动器进行设计时这里提供的材料有助于您更加全面地考虑众多必要因素。理解差分放大器——并在项目开始时就留意ADC驱动器设计的细节——将使设计过程中发生的问题最少,并使您远离ADC驱动器故障。