基于ISL5416的GPS/BD-2接收机DDC设计与实现

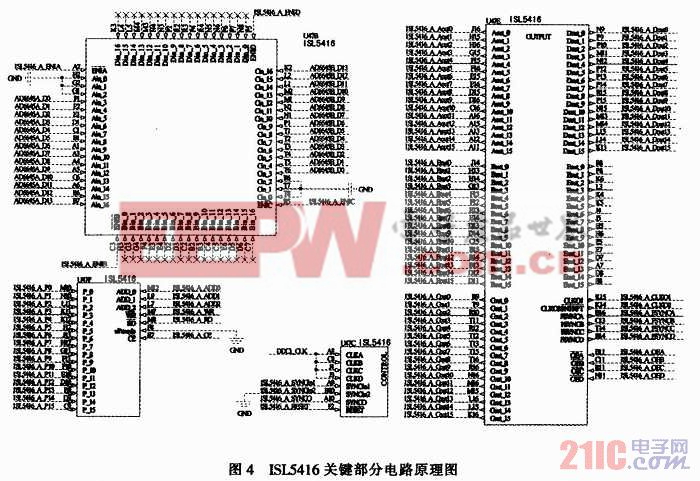

参考ISL5416设计手册根据系统指标,并结合系统设计要求,完成ISL5416各模块的配置和设计如下:

2.2.1 输入和输出接口

ISL5416输入时钟:80MHz,时钟输入引脚CLKC;输入数据格式为16位二进制补码,定点;输入模式为门控(GATED);NCO中心频率为GP-S:12.58 MHz,BD-2:26.902 MHz;ISL5416的输出接口为4组16位并行输出接口,4个下变频通道要同时输出4组I、Q数据则需要8个16位输出接口。因此采用分时复用输出的方式,即在第1个时钟输出GPS基带数据,在第2个时钟输出BD-2基带数据。接口数据率为10 MHz。

2.2.2 CIC滤波

CIC滤波器通带宽度很窄,而且级数越高相对带宽越窄。在相同相对带宽下,级数越高混叠衰减越大。综合考虑,在混叠衰减-100 dB的条件下,CIC配置如下:

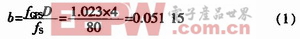

1)GPS CIC级数为5,抽取因子4,输入数据率80 MHz。通带1.023 MHz,计算CIC滤波器的带宽比例因子b为:

参见ISL5416数据手册表可知CIC滤波器通带衰减-0.257 dB,混叠衰减-119.749 dB。

2)BD一2,CIC级数为5,抽取因子4,输入数据率80MHz,通带2.046 MHz,参照式(1)计算CIC滤波器带宽比例因子b为0.102 3,参见ISL5416数据手册上的表可得带宽比例因子为0.10时,通带衰减-0.717 dB,混叠衰减-96.135 dB。

2.2.3 FIR1滤波器

FIR1有32抽头,有20位可编程系数,20位输入数据,24位输出,每个时钟计算4抽头,如需使用全部32抽头则每次计算共需8个时钟。 FIR1的抽取数可以编程为1~8。

由于前级CIC滤波器抽取因子为4,FIR1每次计算只有4个时钟周期,因此可以选择将FIR1配置为16抽头的FIR滤波器,抽取因子为2,输出数据率为10 MHz。GPS和BD-2滤波器设计分别如下:

1)GPs输入数据率20 MHz,通带1.023MHz,截止频率为6MHz,阻带衰减80 dB,通带波纹0.1dB,抽取因子为2,输出数据率降为10MHz。

2)BD-2输入数据率20 MHz,通带2.046MHz,截止频率为7MHz,阻带衰减80dB,通带波纹O.1dB,抽取因子为2,输出数据率降为10MHz。

2.2.4 FIR2滤波器

FIR2有64抽头,有20位可编程系数,20位输入数据,24位输出,每个时钟计算8抽头,如需使用全部64抽头则每次计算共需8个时钟。F-IR2的抽取数可以编程为1~8。由于CIC与FIR1总的抽取因子为8,因此可以使用全部64抽头。GPS和BD-2滤波器设计分别如下:

1)GPS输入数据率10MHz,通带1.023MHz,截止频率为1.6MHz,阻带衰减80dB,通带波纹0.1dB,抽取因子为2,输出数据率降为5MHz。

2)BD-2输入数据率10MHz,通带2.046MHz,截止频率为2.5MHz,阻带衰减80dB,通带波纹0.1dB,抽取因子为2,输出数据率降为5MHz。

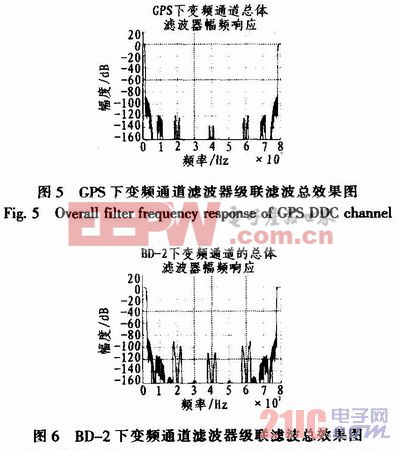

DDC下变频通道,经CIC、FIR1和FIR2级联抽取滤波,3个滤波器级联的总体频率响应如图5和6所示,从图中可以看出带外抑制在90 dBFS以下能够满足实际要求。

3 性能测试

3 性能测试

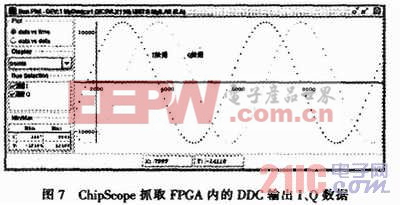

本系统采用AD6645高速ADC采集数据,并将数据输入ISL5416。通过XILINX公司的XC5VLX110,百万门级的FPGA接收DDC下变频后数据。调试时,通过FPGA调试工具软件ChipScope抓取FPGA内ADC数据及ISL5416输出的I、Q两路数据。FPGA内的DDC输出I、Q数据如图7所示。由图可见,ISL5416正确地输出了正交的I、Q两路信号。

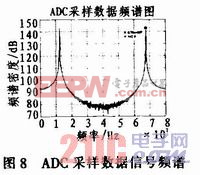

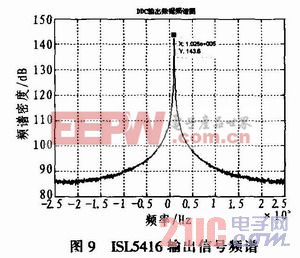

采用安捷伦信号发生器33250A产生67.52 MHz单频正弦信号,在ADC采样率为80 MHz时,采样得到信号频谱如图8所示。信号经ISL5416下变频之后得到I、Q两路数据,I、Q两路数据合成的复信号频谱如图9所示。

从以上两图可以看出,67.52 MHz单频正弦经80 MHz采样,ISL5416按上文所述的配置工作,频谱搬移67.42 MHz,输出正交的I、Q两路信号,I、Q两路信号的频率为100 kHz,实现了频谱的搬移,阻带抑制符合要求,ISL5416正常工作,实现数字下变频。

4 结 论

本文根据工程项目需求,结合4通道专用DDC芯片可灵活配置的特性,合理设计,将接收机中ADC采样后的多载波中频信号,通过DDC通道下变频得到GPS和BD-2的I、Q数字基带数据,以便后续的阵列信号处理及抗干扰算法研究。最终,使用8片DDC芯片ISL5416,实现了16阵元GP-S/BD-2接收机的DDC设计。由于此类接收机阵元数多,各通道结构一致,采用专用DDC芯片节约成本,也避免了采用FPGA设计DDC时的重复设计。为软件无线电在16阵元GPS/BD-2接收机的实现提供了解决方案,并具有较强的商用价值。

DDC 设计 实现 接收机 BD-2 ISL5416 GPS 基于 相关文章:

- 基于DDC和DUC的大带宽DRFM设计与实现(04-24)

- 通信应用中的数字上变频和下变频(04-07)

- 直接变频接收机设计可实现多标准/多频带运行(10-11)

- 基于蓝牙芯片的无线通信模块设计与开发(02-03)

- 无线通信网络设计与现场测试(10-10)

- WiMAX数据传输加密方案设计与实现(05-25)