基于光纤通信的分布式高速高精度数据采集系统设计

摘要:介绍了一个高精度、高信噪比的远距离分布式多通道数据采集系统的设计方法。该系统由前端采集模块和后端解算卡组成,其中前端分布式采集模块负责对模拟信号进行采样并在抗混叠数字滤波后,通过光纤通道将数据传给后端的实时解算卡做进一步的并行解算与分析处理。经最小二乘曲线拟合法测试表明,该采集系统的采样误差小于0.1%。

关键词:光纤通信;分布式;高精度;数据采集;CompactPCI Express

0 引言

瞬态信号捕获的测试测量工程应用中,通常要求测试设备能够满足高速高精度的数据采集任务,同时被测量信号应分布在一定距离范围内。这就要求测试设备能够执行分布式的采集与传输任务。此外,每个分布点的模拟信号可能有多种类型,因此,单个分布点处的采集模块又需要多通道并行采集。为此,本文给出了基于光纤通信的高性能分布式数据采集系统的设计方法,同时描述了设备的设计、实现及其采样精度的验证方法。

1 分布式系统架构

本系统的整体结构分为前端和后端两部分,前端是分布式的采集模块,后端采用改进的Compact PCI Express背板传输结构,两部分之间通过光纤通信,图1所示是其结构示意图。

在系统前端,采样点分布在较长距离范围内,每个采集模块的设计集成了六个通道,每个通道的16位AD采集率按要求要达到4MSPS,总共的数据量可达到48MB/s,如此大的数据量,一方面要求传输总线的容量要足够大,另一方面要求数据不能因传输过程中的外界噪声而出现高误码率。鉴于此,本设计采用分布式采集、光纤通信的设计方案。这样既能满足高带宽要求,又能使数据(光信号)在传输中不受外界噪声(电信号)影响,从而达到高速高质量数据传输的目的。本设计中每个采样模块都连接有一对光纤通道:其中一根用于下行发送同步信息和配置命令,另一根用于上行传输数据和模块当前配置信息。

本系统后端采用改进的CPCI-E背板结构,它集成有CompactPCI (CPCI)、CompactPCI Express (CPCI-E)和实时触发总线等三种总线。其中CPCI总线用于低速传输以及兼容已有功能卡产品;CPCIE总线用于高速数据传输;实时触发总线用于系统内各种板卡的精确同步。本系统内有一张4路PCIE x1的背板,故允许四张实时解算卡同时在系统内工作。每张卡上根据需要又可挂1~4个采集模块。处理卡通过PCIE与主机通信,并通过实时触发总线与系统内其他功能卡同步。实时解算卡向下可通过光纤发送同步信息和配置命令,并对前端由光纤传来的数据进行并行处理,以得到一些参数性的结果,同时也可以将原始数据通过PCIE传输给主机显示并存储。

因此,这种分布式的系统结构能有效地解决远距离分布点的多通道采样、数据的高质量高速传输、大量数据的并行实时处理等工程问题。

2 系统设计

2.1 采样电路设计

系统中的采样电路采用ADI公司的16-bitPulSAR差分ADC芯片AD7625,该芯片的采样率最高可达6MSPS,具有93dB的优秀信噪比。

AD7625的采样控制与数据输出引脚为串行LVDS接口,可与FPGA上具有LVDS特性的IO口直接相连。AD7625与采样相关的引脚有CNV+/CNV-(IN)、CLK+/CLK-(IN)、D+/D-(OUT)三对LVDS差分信号线。由于前端模块设计为6通道并行采样,因此,可采用自时钟接口模式(SelfClocked Interface Mode),因为这种模式下可使所有通道共用CNV与CLK信号,因而可节省不少引脚和布线空间。

采集模块的光纤接收端每收到4MHz的同步采样信息即开始启动一次AD转换,并读取上一次的转换结果,同时在形成帧结构后,再由光纤

发送端上传到系统后端。AD7625的采样时序如图2所示。

完成同步采样逻辑后,可使用嵌入式逻辑分析仪的工具Chipscope抓取FPGA内部逻辑的采样控制信号及采样结果,并显示出来,图3所示的窗口显示的就是采样结果波形,下面的窗口为启动一次AD转换后,FPGA内部的采样控制信号的时序。

2.2 光纤通信

光纤通信可选用AVAGO公司的AFBR57M5APZ型光纤通道收发模块,它的传输线速率可达到2.125Gb/s。每个前端采集模块的总采样数

据量为48MB/s,因此,经过8B/10B编码后,即是480Mb/s的线速率。另外,由于还需要上传前端模块当前的配置信息,因此,应将光纤的线速率定为500Mb/s。

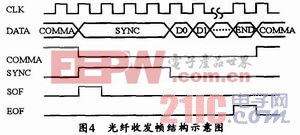

光纤模块可与FPGA中的RoeketIO直接连接以实现高速通信。图4是FPGA内光纤收发模块的帧结构示意图,而其光纤收发时序如图5所示。

2.3 数据实时处理设计

在系统的后端,实时解算卡上FPGA内的数十个DSP核可对光纤通道接收到的高速数据进行并行解算,以得到部分波形参数,然后由上位机

软件据此进行二次计算,便可得到所有波形参数。此外,在实时解算卡上还有大容量的DDRSDRAM,可以使每根光纤上传来的数据缓存数十秒钟,也就是说:上位机软件可以捕捉宽达数十秒钟的数据回放,亦可实时显示某张卡的原始波形。

3 采样精度测试

测试信号源可使用Agilent公司的33250A型信号发生器,该型号在DC~20 kHz频率范围内所产生的波形总谐波失真度为0.04%(即万分之四)。信号源输出与测试电路之间可用50欧阻抗的同轴电缆相连接。

测试方法采用曲线拟合法,即由软件基于时域的原始数据,并用最小二乘法拟合出理想(无谐波失真)波形,再由理想波形与采样原始数据做差后放大100倍生成一条新的曲线,然后计算该曲线幅度与原始波形幅度的相对大小,即可准确反映系统采样误差的大小。

数据采集 系统 设计 高精度 高速 光纤通信 分布式 基于 相关文章:

- 基于GPS的数据采集系统的研究(01-15)

- 无线射频识别技术在规模化奶牛场的应用(05-14)

- 瑞风智能一卡通社区解决方案(05-15)

- 短波发射机自动功率控制异常波形采集系统设计(08-29)

- 简易数字存储示波器的设计(07-24)

- 基于RFID技术的核心物品实时监控管理系统(05-31)