短波发射机自动功率控制异常波形采集系统设计

摘要:短波发射机自动功率控制中,算法设计缺陷或反馈控制系统故障可能导致输出波形失真,甚至产生毛刺,损坏发射机功放或降低功放输出效率。针对短波发射机自动功率控制波形检测采集分析中的数据交互量大、实时性要求高等特点,提出了一种自动功率控制异常时波形实时采集设计方案。实验表明,本设计不仅灵活可靠,且能满足大量数据的实时交换要求。

引言

音频信号进入发射机经过调制后,通过信道功率控制使调制信号输出电压值逼近功放理想输入值,从而提高功放效率。信道功率控制主要包括自动增益控制(AGC)与自动电平控制(ALC)。

实际工作中,调制信号经过信道功率控制后会有各种不同的瞬态响应,可能产生毛刺或发生包络失真,从而降低通信质量,增大误码率,严重的可能损坏功放[1]。分析射频信号的毛刺等高频信号的变化特性、功率上升时间、包络长期稳定性等参数,发现射频信号采集分析系统可以检测通信设备功率控制中是否存在设计缺陷或发生故障。这对于保证通信质量和保护功放,具有重要意义。

由于毛刺等高频信号的变化特性往往是瞬态的,因此,对采样检测系统的采样率和处理速度提出了较高要求。此外,由于信号包络变化慢,延续时间长,因此,包络失真检测系统的存储容量足够大。

为实现整个系统功能,需要FPGA和DSP作为下位机,以完成毛刺检测这类“高频”信号特征检测,并可将发现的异常波形标记后返回上位机。另外,由PC完成大存储量、低速的“低频”信号特征(包络失真等)检测。上位机与下位机之间的数据交互量大,实时性要求高,因此,需要一种数据传输更为可靠、传输速率更快的上位机与下位机之间的通信方案。

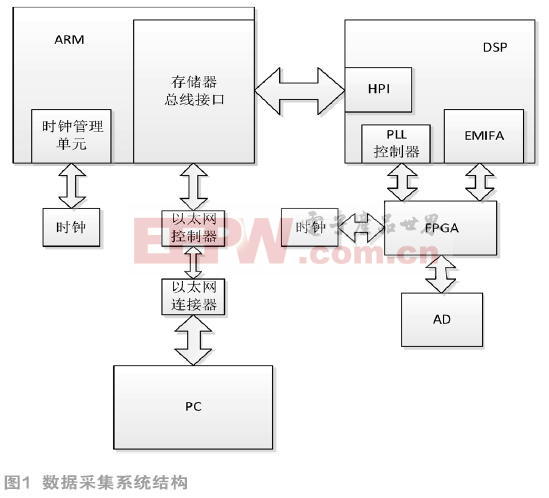

本文设计了一款可实现上位机与下位机大量数据实时传输的通信系统。下位机由DSP与FPGA构成,完成数字信号的初步处理,其中DSP完成复杂算法及控制任务,FPGA完成实时性要求高、运算量大的毛刺识别等高速信号处理。上位机程序则利用MATLAB编程,完成实时性要求不高但数据量较大的信号处理及显示控制任务。上位机与ARM之间通过以太网连接,基于UDP协议实现。ARM通过HPI接口控制DSP,实现数据采集和命令控制。

1 总体设计

1.1 系统结构

PC机的各类并行总线通常无法直接连接机外高速并口设备,如各类DSP的高速主机接口(HPI,Host Port Interface)。本文采用ARM作为DSP与PC之间的桥梁。PC与ARM之间采用以太网通信方式,ARM与DSP在同一电路板上集成,从而解决了并行高速总线的连接问题,使系统设计简洁,应用方便,同时满足高速数据传输的要求。

图1显示了系统的硬件结构框图。从图1中可以看出,上位机通过网线连接ARM,ARM控制DSP的主机接口,AD采样的大量数据经过FPGA做相应处理后返回给DSP的EMIF接口。数据采集系统中,FPGA与ARM由各自晶振提供时钟,FPGA对晶振频率做锁相处理后给DSP和A/D提供时钟。

系统中,ARM控制板基于TI公司的LM3S9B96芯片;FPGA采用ALTERA公司StratixⅡ系列的EP2SGX30D;DSP选用了TI公司的TMS320C6416。

1.2 工作流程

上位机与DSP完成一次通信的工作流程如图2所示。从上位机发出的命令被处理成UDP报文形式后,经过以太网连接器与控制器进入ARM,再经过UDP协议解析后被转发送至DSP。由于ARM直接控制HPI接口,因此,命令转发过程即是ARM改写DSP的RAM空间的过程。DSP收到命令后将解析报文,执行命令。执行完命令后,DSP将要返回给上位机的数据写到之前定义好的RAM空间内。ARM之后将访问DSP的RAM空间,即进行读操作,将该数据整理成UDP报文形式,并通过网口转发给上位机。DSP与ARM之间采用中断方式通知对方新数据或命令的到来。

2 硬件设计

2.1 ARM控制板设计

ARM开发板硬件设计如图3所示。本设计中的ARM开发板是基于TI公司的LM3S9B96芯片,其硬件模块主要包括1个看门狗复位电路、1个网络变压器以及2个晶体振荡器。

LM3S9B96的时钟来源是主振荡器(MOSC)或16MHz内部振荡器(IOSC)。最终产生的系统时钟用于Cortex-M3处理器内核以及大多数片内外设。本设计中,主振荡器通过外部单端时钟源连接到OSC0输入引脚,以提供频率精准的时钟源。

看门狗复位电路是一个定时器电路。正常工作的MCU每隔一段时间输出一个复位信号到看门狗复位电路输入端,给WDT清零。若超过规定时间未发送复位信号(一般在程序陷入死循环时),WDT定时超过后,看门狗电路就会发出一个复位信号到MCU,使MCU复位,防止MCU死机[2]。

LM3S9B96芯片集成了MAC和PHY功能,只需要连接集成变压器的RJ45网口和必要的阻容器件,便可以实现以太网通信。

2.2 DSP主机接口(HPI)设计

上位机通过ARM可访问主

数据采集 异常波形检测 自动功率控制 发射机 短波 201609 相关文章:

- 基于GPS的数据采集系统的研究(01-15)

- 无线射频识别技术在规模化奶牛场的应用(05-14)

- 瑞风智能一卡通社区解决方案(05-15)

- 简易数字存储示波器的设计(07-24)

- 基于RFID技术的核心物品实时监控管理系统(05-31)

- 基于以太网技术和RS-485协议的网络化数据采集系统介绍(09-11)