1553B总线网络存储器设计方案

时间:08-22

来源:互联网

点击:

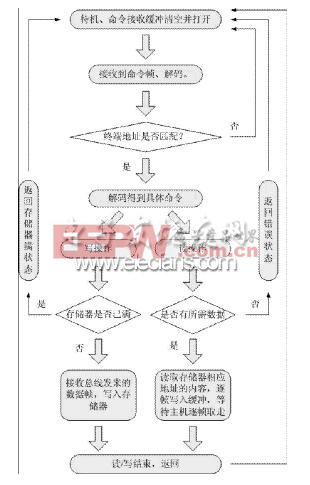

加至NIOS II内核中。FPGA内部的工作流程如图3所示。

图3 FPGA内部工作流程

系统平时处于待机状态,当命令帧到来时会引起中断,中断子程即通过altera_avalon_1553B_getframe()解读命令帧的内容,确定是读取还是写入,读取或写入数据的长度,数据的特征作为下次读取的标志,确实无误后,开始读取或写入。

存储器的管理与其他应用中不同的有两点:在每次写入后,必须将写入的数据作一个标志,以方便以后读取;另外,还要计算剩余存储的容量,在下一次需要写入数据时判断是否可以容纳下本次存储。1553B的主结点在使用完毕数据后也需要提供信号来清空存储以释放资源。

- 直接变频接收机设计可实现多标准/多频带运行(10-11)

- 基于蓝牙芯片的无线通信模块设计与开发(02-03)

- 无线通信网络设计与现场测试(10-10)

- WiMAX数据传输加密方案设计与实现(05-25)

- 高性能TD-SCDMA接收机的设计(03-15)

- 初步设计WiMAX射频系统(03-29)