音频信号数字化光纤传输实验仪信道的设计与实现

摘要:介绍音频信号数字通信实验装置设计的实现过程,该装置以FPGA为主控芯片,以光纤为通讯媒介,将音频信号数字化后通过光纤实现传输,并对电路各个模块的功能及实现加以说明实验装置采用分模块式的设计,设计思路灵活,结构清晰。电路在Altium Designer和Prote 199中设计完成,并且在QuartusⅡ环境下用VerilogHDL语言进行编程并对程序进行仿真。该装置已做成了实体,可以实现音频信号的发射与接收,达到设计提出的要求。

关键词:音频信号;数字信号;FPGA;光纤通信;VerilogHDL

随着光纤技术的不断发展,光纤的应用越来越广泛。光纤以其频带宽、容量大、衰减小等优点给通信领域带来的改革和创新,形成了一个新兴产业。数字通信对比传统的模拟通信有精度高、灵活性高、可靠性强、易大规模集成、时分复用、功能稳定等优点而被广泛的应用在工业、医疗、军事等诸多领域。数字光纤通信兼有两者的优点,必将成为通信领域的发展方向。

音频信号的光纤传输有快速、准确、信息量大、质量高的优点。在实验领域,可以快速准确的传递声音信号,给实验者更可靠的信息。在应用领域,可以实时、长距离传递声音,即节约成本,又有高的传输质量。因此,音频信号的光纤传输的研究与实现,将方便人们的学习、工作和生活。

文中是针对普通高等工科类学校中非通信与信息等专业学科的普及性实验教学科目所研制的《音频信号的数字光纤通信实验仪》创新实践项目。教学科目及实验仪器的推出,有利于帮助高等学校基础性学科实验课程的提升,丰富与完善实验课内容,使学生了解现代技术的发展与相关知识的掌握。

1 系统的硬件结构

信号通道由两大部分组成:光接收器和光发射器。两者之间以光纤连接。光发射和光接收器的工作原理相互关联,一个是另一个的逆过程;光发射器是将音频的电信号转变成光信号,光接收器是将光信号转变成音频的电信号。

光发射器由以下几个电路模块组成:滤波放大、A/D转换、控制部分、并/串转换、电/光模块部分。

光接收器由光/电转换部分、串/并转换、控制部分、D/A转换、模拟信号放大部分组成,如图2所示。

2.1 电 源

整套电路仅以12 V直流电源供电,内部集成电路需用到5 V、3.3 V、1.5 V的电源。5 V电源由L7805三态稳压电源提供.3.3 V和1.5 V分别由ASM117-3.3和ASM117-1.5提供。

2.2 FPGA的数据处理及实时控制部分

电路采用型号为EP1C3T100C8的FPGA为主控芯片,直接由18.432 MHz的晶振提供工作时钟。芯片共有两个时钟输入端,选其一输入晶振时钟。由于FPGA各个模块都用到,所以各个模块都需要供电和接地。

FPGA内部有一个锁相环,可以进行分频和倍频,以得到不同的频率。发射器中模数转换芯片和并/串转换芯片的时钟由FPGA提供。由于模数转换后输出串行的二进制数据,而并/串转换器的数据输入为10位,所以需要在FPGA中进行编码。编码应尽量避免多个“0”和“1”连续出现,采用8810B编码方式。FPGA内部先将串行二进制数据分解为8位并行数据,再经过8810B编码输出。接收器中FPGA提供数模转换器工作时钟和串并转换器的参考时钟,并将串并转换器输出的十位数据解码,还原为八位数据传输给数模转换器。FPGA的功能由Verilog编程实现,程序采用AS(主动)配置方式下载到FPGA。

2.3 音频信号的处理及采集

音频信号经声道分离、滤波、放大,由模数转换集成芯片采集转换成数字信号。

2.3.1 滤波放大部分

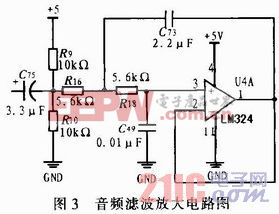

在对音频信号进行采样时,当信号中含有大于二分之一的采样频率,如果采样频率不够高,就会产生混叠信号。混叠信号不能用数字滤波方法除去,需要用硬件滤波。A/D转换的采样频率需要高于音频信号最高频率的2~10倍。根据所需音频信号的带宽以及抗混叠滤波所需要的特性,设计一个二阶的低通有源滤波器,截止频率大于或等于20 kHz,设计电路如图3所示。

同时,该电路具有隔离放大作用,集成运放采用的是单电源供电的LM324。这是一款四运放集成、功耗低、电压工作范围宽的放大器。它具有内部补偿的能力和较低的输入偏置电流。工作于5 V电源时具有1.2 MtIz的带宽。由于音频信号是两路输入(或多声道),且人耳能够分辨的声音带宽为20Hz~20 kHz,所以LM324足以满足要求。电路如图3所示,此为单侧声道,另一声道与其相同。

图中LM324采用5 V电源供电,一级放大。信号输入时要加人一定的电压偏置。

2.3.2 A/D转换部分

模数转换电路采用了Cirrus Logic公司出品的专业音频处理集成芯片CS5342,其工作时钟频率设定为18.432 MHz,由FPGA提供。信号由AINL和AINR管脚输入,SDOUT输出转换后的串行二进制数据,LRCK和SCLK输出采样频率。M0和M1脚分别接高、低电平,以保证芯片工作在双倍速主动模式上,分频产生采样频率96 MHz。另外,RST脚置高电平,各类参考电压引脚加入适当的滤波电容,使芯片稳定且正确地工作。其电路如图4所示。

信道 设计 实现 实验仪 传输 信号 数字化 光纤 音频 相关文章:

- 基于McWiLL的基站信道资源的分配(01-30)

- 测量WiMAX信道功率的有效方案(06-30)

- 基于3G的MIMO技术(06-28)

- 电视频段 无线宽带“拓荒”(12-12)

- McWiLL宽带基站的信道管理(12-12)

- LTE系统时延及降低空口时延的4种方案(06-28)