一种低误码率的ADS-B接收机的设计

示。

3 软件设计

3.1 总体设计

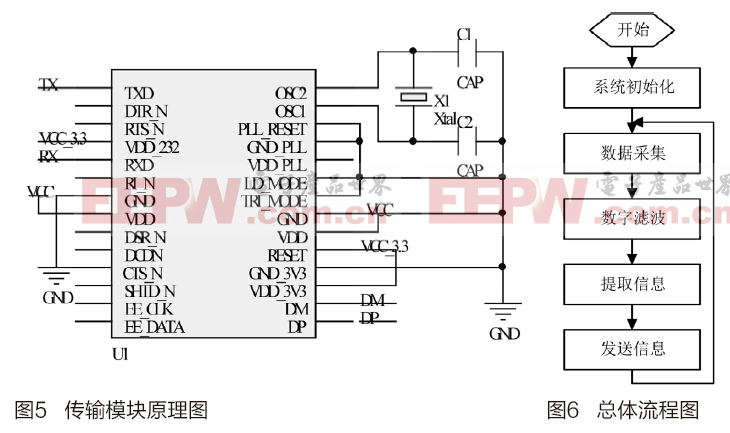

软件设计包括ADC数据读取、数字滤波、信息提取、CRC校验、串口发送等几个部分。通过读取前端信号,并滤除相关的干扰信号,得到平滑信号,提取相关信息发送到上位机中。由于FPGA 并行处理的特点,所以数据的滤波和数据的提取是流水线的处理方式;数据格式的转换采用的是连续型赋值的方法,保证数据随时更新;同时,数据的发送是独立进行的,通过是否存在存储数据来判断是否发送;其流程图如图6所示。

3.2 信号提取设计

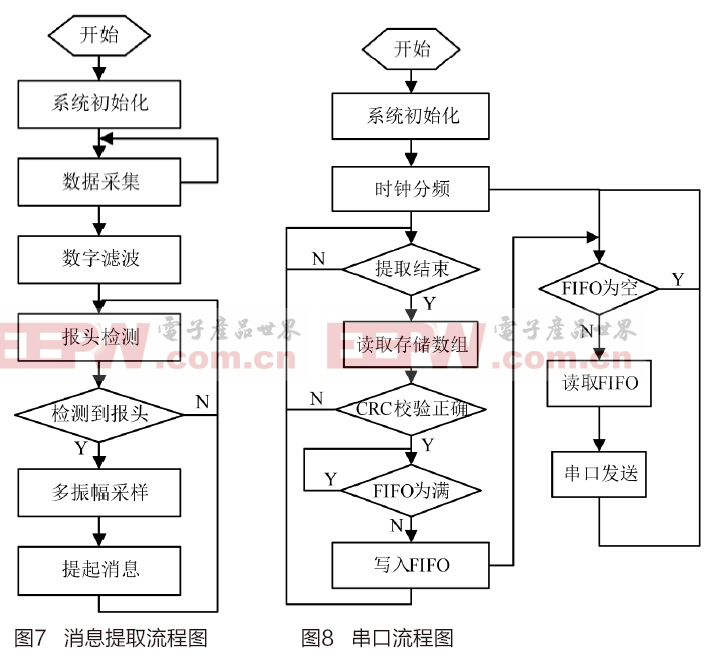

ADS-B的信号经过数字滤波之后,去掉干扰成分。在模式S应答处理中,首先要完成的操作是报头检测,它是一切后续处理的前提和基础[3],信号的提取主要是检测信号的报头起始部分,即检测四个有效脉冲;检测到报头之后提取信号的有效功率,通过多振幅采样点方法[5]计算代码,提取112位或56位消息。其流程图如图7所示。

3.3 串口程序设计

通过FPGA实现串口的设计,需要将数据送入FIFO中,然后从FIFO读取相关的数据,发送到上位机中,保障数据的完整性。为了保证数据读写速率相同,这里的FIFO采用了读写时钟同步的FIFO读写方式。在得到信号提取接收信号之后,读取存储ADS-B信息的数组,然后进行CRC校验,如果校验正确,转化为ASIC II码,将数据写入FIFO中,并改变FIFO的存储状态;同时,串口发送部分通过判断FIFO的状态信号来判断是否发送信息,如果FIFO为空,则等待不为空信号;否则发送相关数据。具体流程图如8所示。

3.4 RTL级原理图

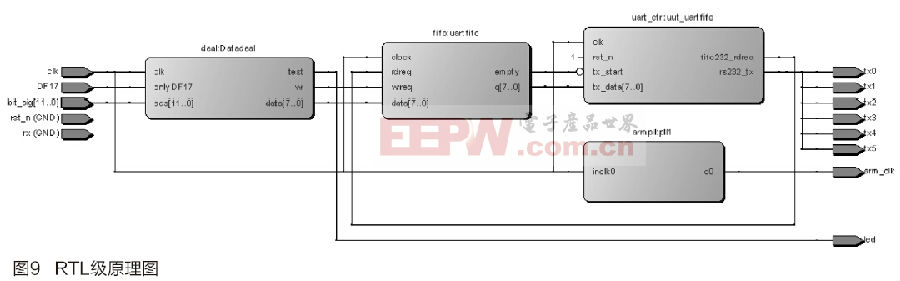

使用Verilog编写了FPGA的实现程序,共包含数据处理部分、FIFO读写部分、串口发送部分和PLL部分,实现ADS-B信息的数字滤波、数据信息提取、数据读写和数据发送的功能。其RTL级原理图如图9所示。

4 实验结果

利用MATLAB读取接收机经过模数转换之后的数据,并通过MATLAB GUI界面显示,获得图10中的滤波前的信号;经过MATLAB编写中值滤波算法实现仿真验证,测试中值滤波在ADS-B信号滤波中的实际效果,得到了图10滤波之后的波形。从图中可以看出中值滤波,能够消除信号中的杂波干扰,使信号变得平滑,并且不改变信号的信号宽度和信号位置,仅仅消除了信号中的杂波干扰信号。

利用串口调试助手验证滤波效果,在相同波特率下,经过滤波之后的信号CRC校验正确的数据要比对比实验组的数据量大,由此可以看出该设计可以降低接收机的误码率。

5 结论

本文介绍的基于FPGA的ADS-B接收机的设计方法,采用了高速ADC转换电路,通过数字滤波算法实现了信号的滤波,消除了杂波的干扰,采用了多振幅采样点方法提取消息更加精确。系统采用了数字滤波的方法,降低了ADS-B信号的误码率,提高了设备的精确度。

参考文献:

[1] 张天平,郝建华,许斌,等. ADS-B技术及其在空管中的发展与应用[J].电子产品世界. 2009(06):34-37+43

[2] 中国民用航空局.中国民用航空ADS-B实施规划[Z].2012-11

[3] 郑植,练马林,张超,等.模式S应答处理中报头检测算法的研究与实现[J]. 电子科技大学学报. 2008(S1):66-70

[4]孙宏琦,施维颖,巨永锋.利用中值滤波进行图像处理[J]. 长安大学学报(自然科学版). 2003(02):104-106

[5] 刘晓斌.基于模式S的ADS-B接收机系统算法研究[D].电子科技大学,2011

ADS-B FPGA 1090MHz 201506 相关文章:

- 基于FPGA的短波通信接收机(11-19)

- FPGA的低功耗设计(07-06)

- EDA环境衔接测量软件(06-25)

- Altera 28nm FPGA助力NEC提升LTE基站性能(11-19)

- 基于FPGA的BPSK信号载频估计单元设计(09-02)

- FPGA推动5G异构无线网络(09-28)