一种低误码率的ADS-B接收机的设计

摘要:针对广播式自动相关监控(ADS-B)接收机存在高误码率的问题,设计一种基于FPGA的ADS-B接收机,通过ADC电路转换解调后的模拟信号为数字信号,并利用FPGA的并行处理的特点,采用流水线方式处理ADS-B信号;利用有关数字滤波和数字信号提取算法,计算得到ADS-B信息,并经过PL2303HX发送电脑上位机中。实验结果证明,可以较好地完成1090MHz ES ADS-B信号的接收,实现了内部数字信号滤波算法和CRC校验,有效地降低设备的误码率。

1 序言

广播式自动相关监视(ADS-B)是一种基于GPS全球卫星定位系统和空-空、地-空数据链通信的航空器运行监视技术[1],正在逐渐成为空中交通管制的一种重要监视手段。ADS-B技术将卫星导航、通信技术、机载设备以及地面设备等先进技术相结合,提供了更加安全、高效的空中交通监视手段,能有效提高管制员和飞行员的运行态势感知能力,扩大监视覆盖范围,提高空中交通安全水平、空域容量与运行效率[2]。本文介绍了一种基于FPGA的1090MHz ES ADS-B的设计方法,通过ADC采样解调之后的信号,并通过数字滤波的方法滤除干扰信号,得到真实信号,利用相关的解算算法,提出ADS-B中的信息,并将其发送到上位机中。

1.1 ADS-B消息格式

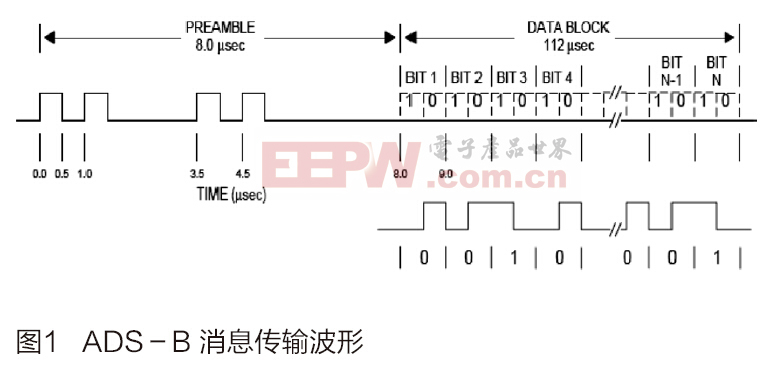

1090MHz ES ADS-B消息包含了四个识别脉冲信号和112位或56位的消息序列。ADS-B消息数据编码格式采用脉冲位置调制(PPM)编码,如图1所示。

1.2 消息提取算法

ADS-B的消息提取采用振幅比较的方法,在该接收机中,采用了10MSPS的采样速率,所以每个信息位前、后时间位置脉冲分别采样5次 [3] 。

(1)将信息位前时间位置的采样集合命名为 ,后时间位置采样集合为

,后时间位置采样集合为 ;

;

(2)计算出SA,SB内在参考功率Ref正负3dB之内的所有采样点:

其中Ref为参考功率,即每个信息位的10个采样点相近振幅最多点的集合;

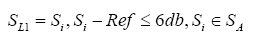

(3)计算出SA,SB内参考功率小6dB以上所有采样点集合:

(4)对以上四个集合的点进行加权运算,考虑到本系统FPGA的性能,所有权值均为整数,其中点S0、S4、S5、S9运算权值是1,点S1、S3、S6、S8运算权值是2,点S2、S7 的运算权值是3,则求的四个运算结果分别为A、B、C、D;

(5)对以上四个运算结果再次做如下运算:

R1= A-B+C-D

R2= B-A+D-C

若R1>R2则该信息位为“1”,否则信息位的值为“0”。

1.3 数字滤波

为了消除ADS-B信号中的杂波,这里采用图像应用中的中值滤波算法。中值滤波的原理是将序列中一点的值,用该点领域内各点值的中值来代替[4] 。

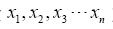

假设 为一组信号序列,按照其大小排序为

为一组信号序列,按照其大小排序为 ,则计算得到其中值数值y是

,则计算得到其中值数值y是

以上公式中,在一维情况下,中值滤波器是一个含有奇数个采样点的滑动滤波窗口[4] 。则滤波器的输出信号序列为:

。

。

2 硬件设计

2.1 系统设计

接收机通过1090MHz 天线接收ADS-B的信号,并通过解调设备,得到解调信号,采用FPGA作为核心处理器,通过AD9233高速ADC转换芯片采集信号,在FPGA中解算提取相关信息。其设计框图如图2所示。

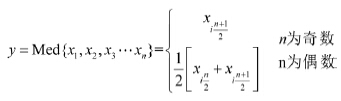

2.2 前端硬件设计

前端设备采用了TA1090EC、BGM1013、TA0232、AD8313芯片,实现滤波和解调的功能,由于后端采用ADC转换电路,所以此处不需要转换为TTL电平信号,最大程度保证信号的完整性和真实性,提高解码的高效性和降低误码率。原理图如图3所示。

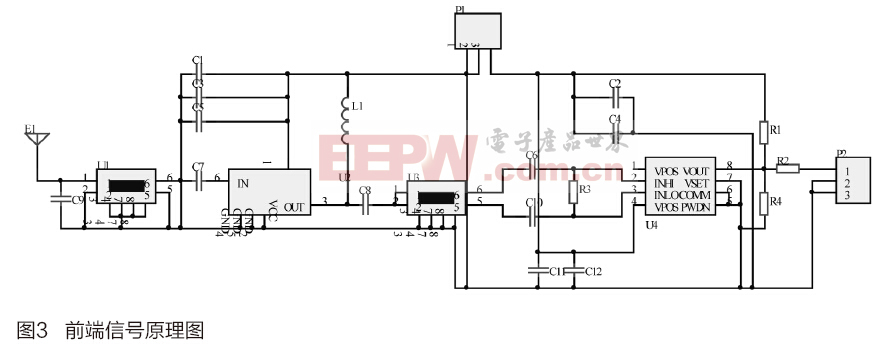

2.3 ADC电路设计

ADC采样电路需要满足10MSPS的采样速率,并且需要保证信号的适当幅度。在这个模块中,采用了ADI公司的AD9233芯片(电路图如图4),其采样频率可以达到125MHz,大大提高ADS-B接收机的信号采集效率;其分辨率为12位,能够很好地识别小信号,还原真实信号,为后面的数字滤波提供数据。

2.3 FPGA电路设计

ADS-B信号的滤波和解码都是通过FPGA实现的。FPGA电路采用Altera公司的EP4CE6E22C8N的芯片,外部通过AMS-1117系列的电源芯片实现3.3V、1.2V、2.5V的供电,并采用EPCS4SI8N作为FPGA的配置芯片。整个系统采用外部有源晶振50MHz作为系统时钟,并通过时钟分频产生ADS-B信号的采样和串口发送的时钟信号。并预留了JTAG和AS的下载接口,以便实现FPGA的调试和下载。整个FPGA在ADS-B接收机中起到了信号的数字滤波、信号报头识别、信号提取、CRC校验、信息转换为ASIC II码和信息的发送等功能是ADS-B接收机的核心。

2.4 传输模块设计

传输模块实现的是FPGA与电脑之间的信息交换。利用FPGA的FIFO进行数据缓存,并通过该模块发送到上位机中。为了提高信息的传输速率,传输模块采用的是PL2303HX,实现了TTL和USB信号的转换,将ADS-B信号转换为AISC II码传递到电脑上位机中。通过上位机解码,提取相关的飞机的位置、速度、高度、经纬度等信息,并显示在界面上,原理图如图5所

ADS-B FPGA 1090MHz 201506 相关文章:

- 基于FPGA的短波通信接收机(11-19)

- FPGA的低功耗设计(07-06)

- EDA环境衔接测量软件(06-25)

- Altera 28nm FPGA助力NEC提升LTE基站性能(11-19)

- 基于FPGA的BPSK信号载频估计单元设计(09-02)

- FPGA推动5G异构无线网络(09-28)